计数器功能模块

计数时钟

计数器的时钟 EPWM_CNT_CLK 由 SYS_CLK 进行分频得出:

EPWM_CNT_CLK =

SYS_CLK / (Divisor1 * Divisor2)

- Divisor1/2 为寄存器 EPWM_CLK_DIV1/2。

- 除数 Divisor1 的可配置范围为 1/ 2/ 4/ 6/ 8/ 10/ 12/ 14。

- 除数 Divisor2 的可配置范围为 1/ 2/ 4/ 8/ 16/ 32/ 64/ 128。

- 开启 EPWM 计数器的计数,需使能全局的控制信号 EPWM_CNT_GLB_EN。

计数方式

寄存器字段 EPWM_CNT_MOD ,可以配置计数器的以下计数方式:

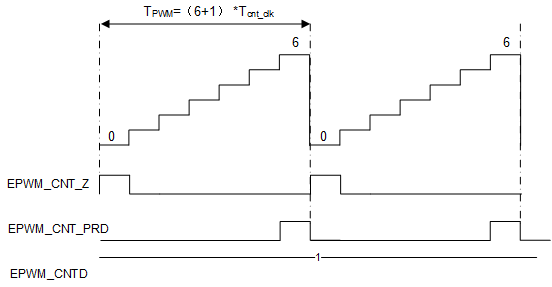

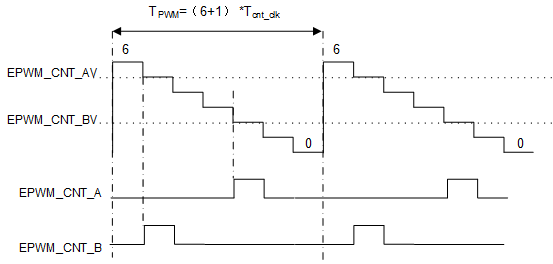

- 递增计数:计数器从 0 开始递增计数,计数至 EPWM_CNT_PRDV 值时,完成一个周期的计数,并且复位至 0

重新开始计数。计数器递增计数图示 中,设置 EPWM_CNT_PRDV = 6 的递增计数,此时开始从 0 到 6 的递增计数:

- 在计数值为 0 时,信号 EPWM_CNT_Z = 1

- 在计数值为EPWM_CNT_PRDV 的时候,信号EPWM_CNT_PRD = 1

- 而指示计数方向的信号EPWM_CNTD 一直为高电平,指示为递增计数。

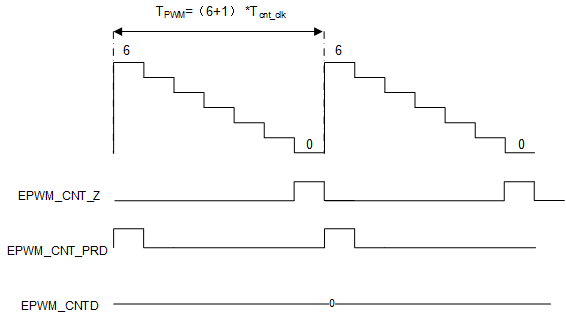

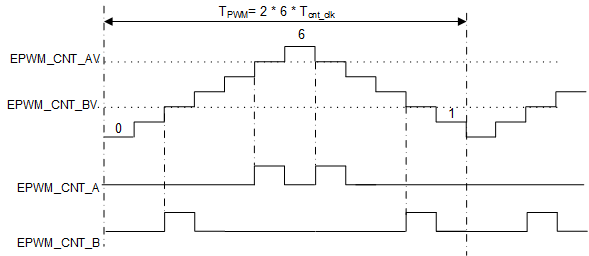

图 1. 计数器递增计数图示 - 递减计数:计数器从 EPWM_CNT_PRDV 开始递减计数,计数至 0 时,完成一个周期的计数,并且复位至 EPWM_CNT_PRDV 重新开始计数。计数器递减计数图示中,设置 EPWM_CNT_PRDV = 6 的递减计数,此时进行从 6 到 0 递减计数:

- 在计数值为 0 的时候,信号 EPWM_CNT_Z = 1。

- 在计数值为 EPWM_CNT_PRDV 的时候,信号 EPWM_CNT_PRD = 1。

- 指示计数方向的信号 EPWM_CNTD 一直为低电平,指示为递减计数。

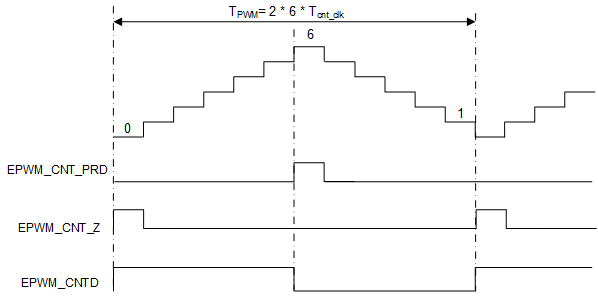

图 2. 计数器递减计数图示 - 先递增后递减计数:计数器从 0 开始递增计数,计数至 EPWM_CNT_PRDV 后进行递减计数,当计数器计数为

1,完成一个周期的计数。下一个周期继续从 0 开始进行先递增后递减计数。计数器先递增后递减计数示例中,设置 EPWM_CNT_PRDV = 6 的先递增再递减计数,此时进行先从 0 到 6 的递增计数再从 6 到 0 的递减计数:

- 在计数值为 0 的时候,信号 EPWM_CNT_Z = 1。

- 在计数值为 EPWM_CNT_PRDV 的时候,信号 EPWM_CNT_PRD = 1。

- 指示计数方向的信号 EPWM_CNTD 在前半周期为高电平指示此时为递增计数,后半周期指示为递减计数。

图 3. 计数器先递增后递减计数示例

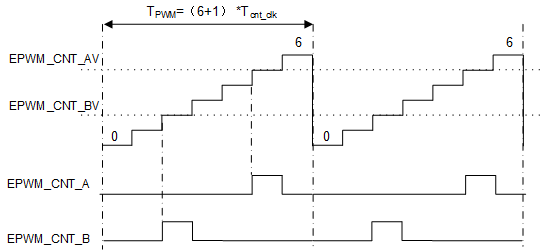

计数比较

在计数数值达到预设的设定值时,即达到 EPWM_CNT_AV 与 EPWM_CNT_BV 时,计数器可以产生相应的信号 EPWM_CNT_A 与 EPWM_CNT_B。

为了区分计数的方向:

- 若为递增计数至 EPWM_CNT_AV 产生的信号,记为 EPWM_CNT_UA。

- 若为递减计数至 EPWM_CNT_AV 产生的信号,记为 EPWM_CNT_DA。

- 若为递增计数至 EPWM_CNT_BV 产生的信号,记为 EPWM_CNT_UB。

- 若为递减计数至 EPWM_CNT_BV 产生的信号,记为 EPWM_CNT_DB。

产生的信号输出至 EPWM 生成模块以及 Trigger & Interrupt 模块使用。具体时序图如下:

计数同步

计数器具有同步的功能,同步信号的使能后,可以使得计数器计数值跳至 EPWM_CNT_PHV 计数同步相位寄存器的数值。

计数器同步信号的来源有两个:

- IN_SYNC,对于 EPWM 子模块,是外部输入信号,各个 EPWM 子模块的 IN_SYNC 的信号来源可参考同步信号网络示例。

- SW_SYNC,为 EPWM 模块通过寄存器设置 EPWM_SW_FRC_SYNC 位而产生,即由软件控制产生。

- IN_SYNC 与 SW_SYNC 的信号经过或逻辑后,决定计数器的同步。

计数器还会产生输出的同步信号 OUT_SYNC,通过寄存器设置可以选择不同的信号作为 OUT_SYNC。同步输出信号源 中展示了 OUT_SYNC 的来源。

EPWM 模块利用输入同步信号以及输出同步信号,将所有子模块 EPWM0/1/.../11

进行计数器的相位同步。同步信号网络示例

展示了各个模块的同步连接方式。

- EPWM0/3/6/9 以及 CAP0 的输出同步信号通过 GPIO_MUX 输出给外部器件,并且进行脉冲的 8*SYS_CLK 的长度延长。

- CPM0_COH 以及 CPM1_COH 分别为 CPM0 和 CPM1 输出的比较信号。

寄存器更新

寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 支持以下更新模式,且各有独立控制的更新模式的控制位。

- 立即更新模式:

- 对寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 的数值写入,会立即生效,从而影响当前的 EPWM 生成。

- 可能出现在当前的周期,新写入的数值与计数器的数值错过比较时刻,导致 AV 和 BV 的动作未发生,进而造成当前周期的输出 EPWM 占空比异常,例如 100% 或 0% 占空比。

- 通过寄存器字段 EPWM_CMPA_IMD_UPDT_PULSE_EN、EPWM_CMPB_IMD_UPDT_PULSE_EN = 1,可以避免立即更新带来的错误 EPWM 输出。

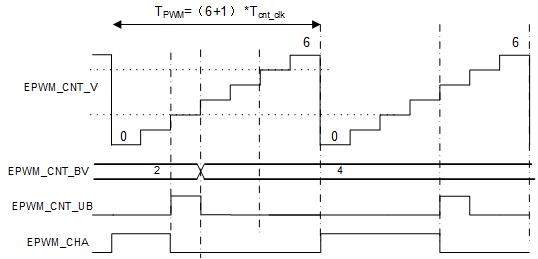

- 影子寄存器更新模式:

- 对寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 的数值的写入,暂时存入各自的影子寄存器,不会立即生效,只有当计数器计数值到指定加载点时才进行更新,影子寄存器的数值生效。

- EPWM_CNT_BV 影子寄存器更新示例中,当对 EPWM_CNT_BV 的数值进行写操作,将数值从 0x2 改变为 0x4 后,并没有立即生效,而是在计数值复位至 0 开始下一个周期的计数后,EPWM_CNT_BV 的数值才生效,从而改变了 EPWM 信号的占空比。

图 9. EPWM_CNT_BV 影子寄存器更新示例