Sigma Delta Filter Module (SDFM)

SDFM,全称 Sigma Delta Filter Module,用于对 1-bit Sigma-Delta 调制的信号进行低通数字处理,进而还原真实信号。常见的比如隔离式 ADC,需要通过 SDFM 进行低通滤波还原获得数字信号,提供给 MCU 进行信号处理。

特性说明

-

外部输入信号 SDIN_DATn、SDIN_CLKn(n = 0/1/2/3)

-

对输入信号支持 3 种解码模式

-

每个 SDFM 模块内部包含两路滤波器:

- PSINC:解析的数据用于用户算法计算

- SSINC:解析的数据用于内部比较,产生触发信号,触发 EPWM 输出保护

-

PSINC 支持 OSR 配置 (1~256),滤波类型配置 (Sinc1/ Sinc2/ Sinc3)

-

PSINC 输出为 16 bits/ 32 bits

-

SSINC 支持 OSR 配置 (1~32),滤波类型配置 (Sinc1/ Sinc2/ Sinc3)

-

SSINC 支持高低双阈值比较

-

支持 FIFO 模式 (64 x 32-bit)

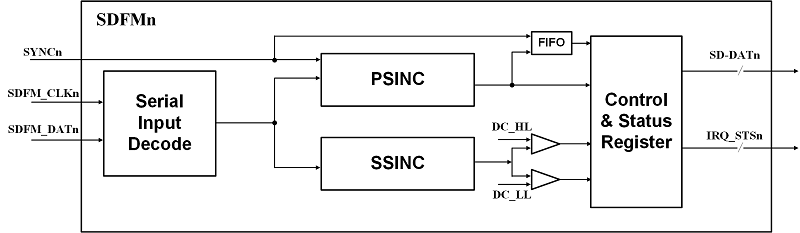

原理框图

-

Serial Input Decode 模块:用于解析串行数据。

-

PSINC 滤波器模块:即 Primary Sinc Filter,主滤波器用于串行数据的数字处理。

-

SSINC 滤波器模块:即 Secondary Sinc Filter,次滤波器用于快速比较,产生比较信号。

-

SYNCn 信号来自 EPWM 的同步信号。