Hardware Current Loop (HCL)

Hardware Current Loop (HCL),硬件电流环 ,实现伺服电机控制的电流环算法硬件化。相对于软件电流环,HCL 具有以下优势:

- 释放更多的 CPU 资源。

- 保证电流环的计算不被打断,提升电流环的带宽。

特性说明

- 硬件电流环计算处理:包括 Clarke 变换、Park 变换、防积分饱和 PID、反 Park 变换、SVPWM 等算法处理

- 支持多种工作模式:Mode0 电流开环、Mode1 电流闭环模式、Mode2 正常工作模式

- 支持断续点工作模式,灵活地支持用户不同的算法需求

- 支持死区补偿算法

- 支持正交编码器和绝对值编码器

- 170 ns 完成一次硬件电流环的计算

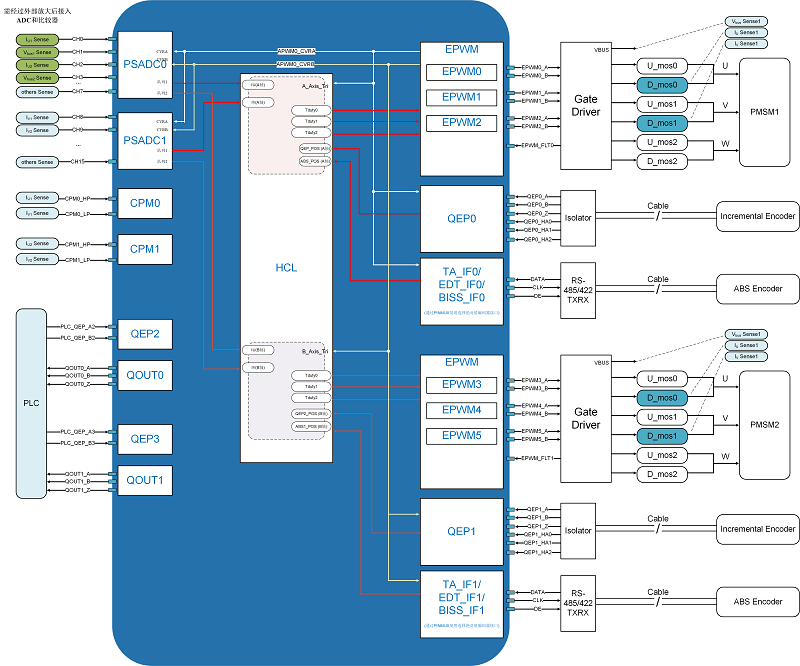

硬件电流环框图

硬件电流环框图中,HCL 电流环算法的一次计算工作流程如下:

- 从 EPWM 触发 ADC0/1 的队列 1 采集电机的 U 相电流和 V 相电流开始,HCL 获取电流数据的同时也进行位置数据的获取 (通过 QEP0 或绝对值编码器接口 0 进行获取)。

- HCL 获取电流数据和位置数据后,依次进行 Clarke 变换、Park 变换、PID 计算、反 Park 变换和 SVPWM,最终完成一次的电流环算法。获得本次更新的 PWM 占空比数据并且自动填写入对应 EPWM 模块的寄存器中。

由于硬件电流环需要其它的硬件资源配合,所以在使用硬件电流环的时候,需要使能和配置所需的硬件资源。

-

ADC0/1 使能,并且需配置队列 1 进行相电流的采样转换。

-

QEP0、TA_IF0、BIS_IF0、EDAT_IF0 需任意选择一种编码器方式,用于获取位置数据。

-

EPWM 需从 EPWM0~6 中选择三路 EPWM 进行三相全桥驱动,并且使能 HCL 自动更新占空比功能。

-

CORDIC 模块使能,由于 HCL 需要触发 CORDIC 自动进行三角函数运算,故需使能 CORDIC 模块。

硬件电流环计算的频率是跟随 EPWM 中 EPWM_ADC_CVRA 触发信号,每次触发信号触发一次 ADC0/1 的采样转换动作、一次的编码器位置读取、一次的电流环计算、一次对 PWM 占空比更新。

实时控制外设互联图——HCL

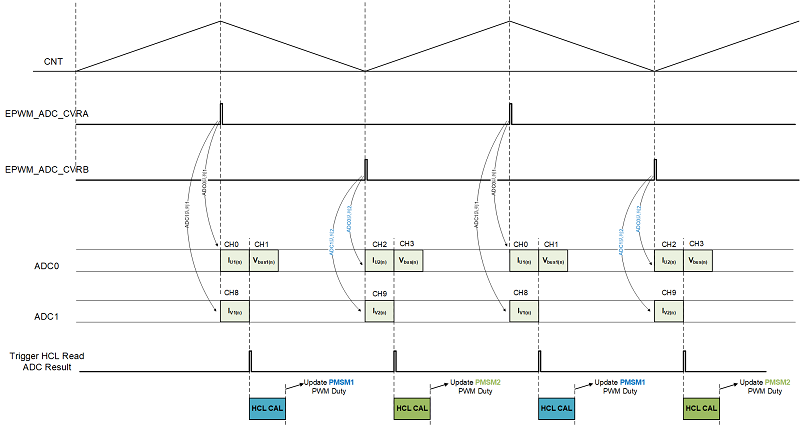

HCL 单轴控制系统框图与控制时序图

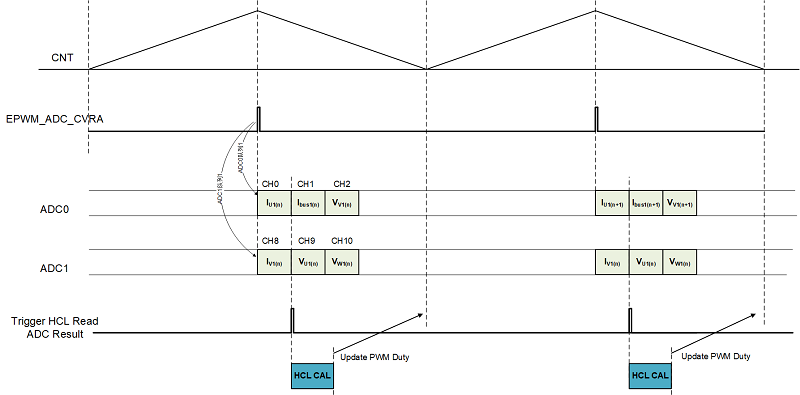

HCL 双轴控制系统框图与控制时序图