功能描述

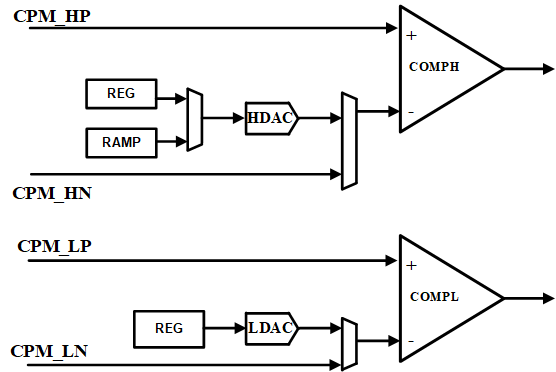

CPM 内置比较器

比较器 |

正端电压输入 |

负端电压输入 |

备注 |

|---|---|---|---|

高位比较器 ( |

外部输入信号 |

可选择外部输入信号 |

当比较器的正端输入电压大于负端输入电压时,比较器输出高电平,否则输出低电平。 |

低位比较器 ( |

外部输入信号 |

可选择外部输入信号 |

DAC 更新模式

高位和低位的比较器各自对配备了一个内置的 12-bit DAC,分别称为 HDAC 和 LDAC。HDAC 与 LDAC 规格基本相同。

以 HDAC 为例,通过配置输出寄存器 DACH_VALS,HDAC 会输出相应的电压 HDAC_OUT。输出电压的计算公式为:HDAC_OUT = VCC33_IO ×(DACH_VALS ÷ 4096),其中 VCC33_IO 是 IO 输入电压。

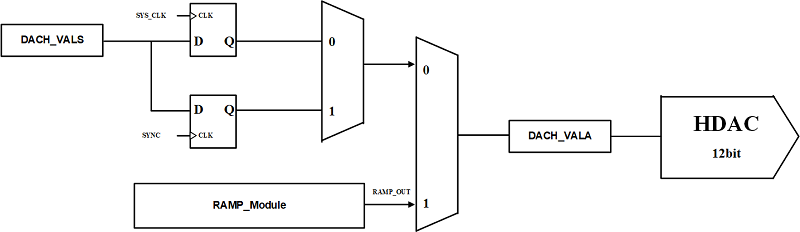

-

HDAC 的输出电压的更新,支持两种模式:寄存器更新和斜坡模块控制更新,如所示。在寄存器更新模式中,可以通过时钟信号 SYS_CLK 或同步信号 SYNC 触发读取影子寄存器更新。斜坡模块的更新方式可参考。

图 2. HDAC 结构框图 -

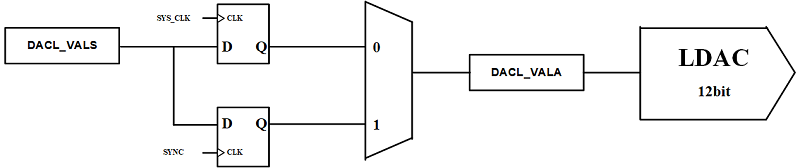

LDAC 的输出电压更新仅支持寄存器更新模式,不支持斜坡模块更新,寄存器的更新模式与 HDAC 的一致。

图 3. LDAC 结构框图

斜坡模块配置

斜坡模块 (RAMP_Module) 用于生成递减的斜坡信号 RAMP_OUT,控制 HDAC 的输出电压。CPM 可以利用此功能生成与输入电压相关的 PWM 信号。例如,在电源应用中,它可以用来控制反馈电压的 PWM 占空比。

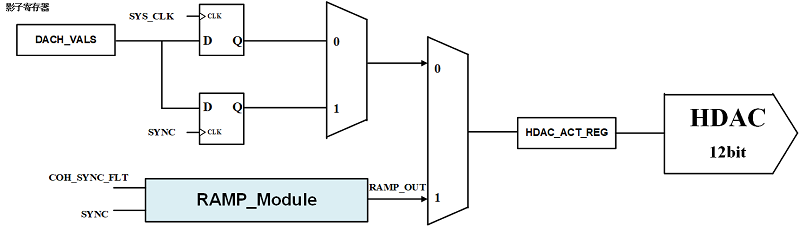

如所示,斜坡模块可以通过以下寄存器配置并结合 SYNC 信号触发,生成精确控制的递减斜坡信号 RAMP_OUT。

寄存器名称 |

功能描述 |

更新方式 |

更新触发信号 |

备注 |

|---|---|---|---|---|

RAMP_MAX_REFS |

设置斜坡信号的起始点。斜坡信号从该寄存器设置的数值开始递减。 |

影子更新 |

SYNC |

无单位,具体数值由应用决定 |

RAMP_DEC_VALS |

设置斜坡信号每次递减的幅度值。 |

影子更新 |

SYNC |

无单位,具体数值由应用决定 |

RAMP_DLYS |

设置斜坡模块启动的延迟时间。 |

影子更新 |

SYNC |

延迟时间为 SYS_CLK 周期数 |

- SYS_CLK:斜坡信号每次递减的时钟频率,由 CPM 模块提供,单位 Hz。

- 影子更新:表示寄存器的更新不会立即生效,而是在同步信号 SYNC 到来时,影子寄存器中的值才会被应用到实际寄存器中。

-

SYNC:同步信号,用于触发影子寄存器的更新。每次 SYNC 到来时,影子寄存器会更新,使用当前的 RAMP_MAX_REFS、RAMP_DEC_VALS 和 RAMP_DLYS 值来控制斜坡信号的生成。

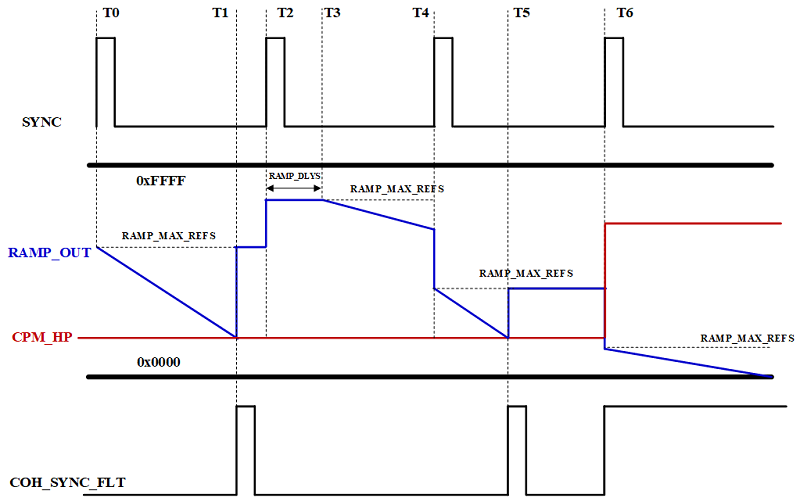

斜坡信号 RAMP_OUT 典型工作时序

以下是斜坡信号 RAMP_OUT 的典型工作时序示例:

时间点 |

事件描述 |

|---|---|

T0 |

SYNC 信号到来,触发 RAMP_MAX_REFS、RAMP_DEC_VALS 和 RAMP_DLYS

影子寄存器更新,斜坡模块启动 (RAMP_DLYS = 0)。 由于 RAMP_DLYS 设置为 0,RAMP_OUT 从当前的 RAMP_MAX_REFS 开始递减。 |

T1 |

RAMP_OUT 控制 HDAC 的输出低于比较器阈值 CPM_HP,CPMH 的输出比较信号 COH_SYNC_FLT

发生翻转,斜坡模块停止递减并将输出恢复到当前的 RAMP_MAX_REFS 值。 HDAC 的输出也回到起始值,比较器的输出再次反转。 |

T2 |

SYNC 信号再次到来,影子寄存器更新,斜坡模块会延迟启动(RAMP_DLYS > 0)。延迟时间为 (RAMP_DLYS × TSYS_CLK ) 。 |

T3 |

斜坡模块启动,RAMP_OUT 开始递减。 在 T3 ~ T4 时间段,RAMP_OUT 尚未低于 CPM_HP 的电压水平,比较器未发生反转,斜坡信号仍在持续递减。 |

T4 |

SYNC 信号到来,影子寄存器更新,斜坡模块继续递减。 |

T5 |

比较器信号翻转,斜坡模块停止并恢复到 RAMP_MAX_REFS 起始值。 |

T6 |

输入信号 CPM_HP 跳变,导致比较器信号反转。SYNC 信号同时到来,斜坡模块继续按照新一轮寄存器值递减。 |

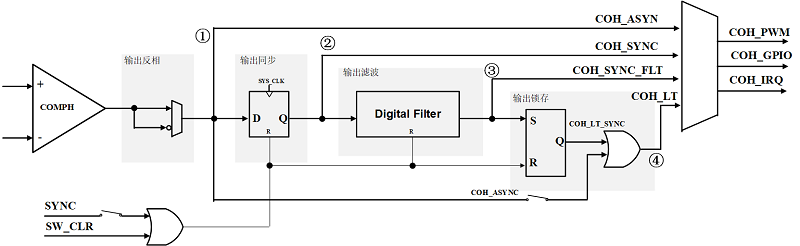

数字输出控制

CPM 模块的数字输出控制逻辑用于处理比较器输出信号,经过多级逻辑操作后,生成可用于 PWM 保护、中断触发或 GPIO 输出的信号。高位比较器和低位比较器的处理逻辑相同。

数字输出控制逻辑流程

以高位比较器的输出为例,数字输出控制逻辑分为四级操作,依次如下:

- 输出异步,此时的信号为异步信号 COH_ASYNC,该通路可以支持输出反相功能。

- 输出同步,采用 SYS_CLK 对比较器的输出信号进行同步,得到同步信号 COH_SYNC。

- 输出滤波,采用数字滤波器,对上级信号进行数字滤波,得到信号 COH_SYNC_FLT。

- 输出锁存,采用 SR 锁存器,锁存输出结果后与 COH_ASYNC 进行 OR 逻辑,得到信号 COH_LT。

数字滤波器

数字滤波器通过采样窗口内的数据判断是否翻转输出信号,等效如下的 C 代码实现:

//当输出为 0 时,检查采样窗口中 1 的数量

if (FILTER_OUTPUT == 0) {

//当采样窗口里数据为 1 的数量大于阈值,则输出信号翻转

if (Num_1s_in_SAMPWIN >= THRESH) {

FILTER_OUTPUT = 1;

}

}

//当输出为 1 时,检查采样窗口中 0 的数量

else {

//当采样窗口里数据为 0 的数量大于阈值,则输出信号翻转

if (Num_0s_in_SAMPWIN >= THRESH) {

FILTER_OUTPUT = 0;

}

}

参数名称 |

描述 |

|---|---|

|

滤波器的当前输出状态 (0 或 1) |

|

采样窗口中值为 1 的数量 |

|

采样窗口中值为 0 的数量 |

|

翻转输出的阈值 例如:采样窗口中 1 或 0 的数量超过该值时翻转输出 |

中断信号

通过寄存器 COH_IRQ_EN/ COL_IRQ_EN 使能,可选择比较器的输出信号 COH_IRQ、COL_IRQ 触发 CPM 中断的产生。

通过配置寄存器的模式位,可以选择具体的触发模式:

-

电平模式:支持高/ 低电平触发中断

当比较器输出信号保持高电平或低电平时,将持续触发中断。

-

边沿模式:支持上升沿/ 下降沿/ 双沿触发中断

在信号由低到高或由高到低的瞬间触发一次中断。