计数器功能

16 Apr 2024

Read time: 1 minute(s)

捕捉模式以及简单 PWM 输出模式,采用相同的计数器模块,使用 32-bit 计数器。

计数时钟

CAP 模块计数器的时钟无分频系数控制,直接由 SYS_CLK 驱动。

计数器在计数值等于 CAP_CNT_PRDV (即 PWM 模式下寄存器 CAP_REG0) 可产生 CAP_CNT_PRD 信号。

计数器在计数值等于 CAP_CNT_CMPV(即 PWM 模式下寄存器 CAP_REG1)可产生 CAP_CNT_CMP 信号。

在计数值达到 0xFFFF_FFFF 时可产生 CAP_CNT_OVFL 信号。

计数同步

CAP 模块的计数器支持外部输入信号同步计数器,并支持输出同步信号。

- 输入同步

当输入同步信号 CAP_SYNCI 有效,计数器将同步相位寄存器 CAP_CNT_PH 的数值加载至计数器,从而达到计数器相位的同步效果。另外 CAP0/ 1/ .../ 5 的输入同步信号的连接方式,可以参考 计数同步。

- 输出同步

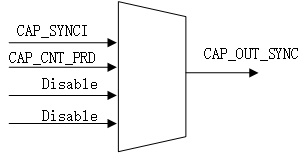

通过寄存器 CAP_SYNC_OUT,可以选择 CAP_SYNCI 信号或 CAP_CNT_PRD 信号输出。