ADC 队列

在 ADC 模块中,采用队列方式进行采样转换。通过寄存器设置队列的采样点数以及每个节点对应的通道,可以精确控制采样过程。

当触发信号到来时,ADC 会根据队列的设置,从节点 0 开始,依次对每个节点进行采样转换,直至完成队列中所有节点的采样转换。

ADC 内置实时队列和常规队列,特点如下:

队列模式 |

优先级 |

特性 |

触发信号 |

|---|---|---|---|

| 实时队列 (Q1, Q2, QC) |

优先级最高,可打断常规队列 QN 的当前请求。 |

实时队列包括队列 Q1、Q2:

|

|

| 常规队列 (QN) |

优先级低于实时队列。 当实时队列有采样请求时,常规队列的任务会被暂时打断,直到实时队列的任务完成后,常规队列才会从被打断的地方继续执行。 |

|

S/W |

实时队列配置

参数 |

描述 |

备注 |

|---|---|---|

Q1/2_TRIG_CNT |

队列采样节点数 |

- |

ADC_Q1_NODE |

各节点对应的采样通道 |

- |

ADC_Q2_NODE |

各节点对应的采样通道 |

- |

ADC_ACQ |

采样时间 |

各个节点可以通过寄存器选择四种采样时间,从而满足不同节点的不同采样时间需求,详情可查看ADC 采样率设置。 |

ADC_ACQ_1 |

采样时间 |

|

ADC_ACQ_2 |

采样时间 |

|

ADC_ACQ_3 |

采样时间 |

|

Q1_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

通过寄存器可以选择进行 2/ 4/ 8/ 16/ 32 倍的过采样。 |

Q2_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

|

ADC_RES_FLTn |

对 ADC 结果寄存器的数据支持进行平均算法滤波。 |

如不需要额外 ADC 数据处理,使用默认值即可。关于详细说明,可查看ADC 数据处理。 |

ADC_OFF_EN |

偏置调整,调整 ADC 转换结果的偏置。 |

如实时队列配置示例所示,队列 Q1 设置采样节点数为 3,节点 1 对 CH5 进行 4 倍过采样,节点 2 对 CH1 进行单点采样,节点 3 对 CH2 进行 2 倍过采样。

双队列模式配置

在实时队列下,可配置 ADC 为双队列模式,即队列 1(Q1)和队列 2(Q2)独立工作,各自最大可支持 12 个节点。

参数 |

描述 |

备注 |

|---|---|---|

Q1/2_TRIG_CNT |

队列采样节点数 |

- |

ADC_Q1_NODE |

各节点对应的采样通道 |

- |

ADC_Q2_NODE |

各节点对应的采样通道 |

- |

ADC_ACQ |

采样时间 |

各个节点可以通过寄存器选择四种采样时间,从而满足不同节点的不同采样时间需求,详情可查看ADC 采样率设置。 |

ADC_ACQ_1 |

采样时间 |

|

ADC_ACQ_2 |

采样时间 |

|

ADC_ACQ_3 |

采样时间 |

|

Q1_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

通过寄存器可以选择进行 2/ 4/ 8/ 16/ 32 倍的过采样。 |

Q2_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

- |

ADC_RES_FLTn |

对 ADC 结果寄存器的数据支持进行平均算法滤波。 |

如不需要额外 ADC 数据处理,使用默认值即可。关于详细说明,可查看ADC 数据处理。 |

ADC_OFF_EN |

偏置调整,调整 ADC 转换结果的偏置。 |

|

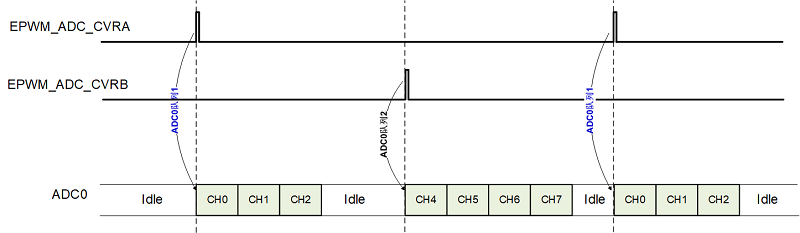

EPWM_ADC_CVRA |

EPWM 产生的触发信号 A,此信号为所有 CVRA 的 OR 逻辑信号 (n=0/1/2/…/11)。 |

Q1 支持的触发信号。 |

EPWM_ADC_CVRB |

EPWM 产生的触发信号 B,此信号为所有 CVRB 的 OR 逻辑信号 (n=0/1/2/…/11)。 |

Q2 支持的触发信号。 |

ADC_TRIGE |

外部的触发信号,通过外部管脚输入。 |

Q1 支持的触发信号。 |

SW_TRIG |

软件触发信号,通过软件写寄存器字段 TRIGS 产生。 |

Q1 和 Q2 支持的触发信号。 |

- 队列 1 设置 3 个采样节点 (Node0~Node2),依次对 CH0、CH1、CH2 进行采样。当接收到队列 1

的有效触发信号后,按顺序完成这三个通道的采样转换,完成后队列 1 任务结束,ADC0 进入空闲状态。

由于队列 1 里设置 3 个采样节点,所以队列 1 中的 Node3~Node11 都不会生效。

- 队列 2 设置 4 个采样节点 (Node0~Node3),依次对 CH4、CH5、CH6、CH7 进行采样。当接收到队列 2

的有效触发信号后,按顺序完成这四个通道的采样转换,完成后队列 2 任务结束,ADC0 进入空闲状态。

由于队列 2 设置 4 个采样点,所以队列 2 中的 Node4~node11 都不会生效。

合并队列模式

在实时队列下,可配置 ADC 为单队列模式,即 Q1 和 Q2 进行合并而成的 QC 队列,最大支持 24 个节点。

参数 |

描述 |

备注 |

|---|---|---|

Q1_TRIG_CNT |

队列采样节点数 |

- |

ADC_Q1_NODE |

0~11 节点各自对应的采样通道 |

- |

ADC_Q2_NODE |

12~23 节点各自对应的采样通道 |

- |

ADC_ACQ |

采样时间 |

各个节点可以通过寄存器选择四种采样时间,从而满足不同节点的不同采样时间需求,详情可查看ADC 采样率设置。 |

ADC_ACQ_1 |

采样时间 |

|

ADC_ACQ_2 |

采样时间 |

|

ADC_ACQ_3 |

采样时间 |

|

Q1_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

通过寄存器可以选择进行 2/ 4/ 8/ 16/ 32 倍的过采样。 |

Q2_SMP_SETn |

过采样设置,各节点默认采用单点采集。 |

- |

ADC_RES_FLTn |

对 ADC 结果寄存器的数据支持进行平均算法滤波。 |

如不需要额外 ADC 数据处理,使用默认值即可。关于详细说明,可查看ADC 数据处理。 |

ADC_OFF_EN |

偏置调整,调整 ADC 转换结果的偏置。 |

|

EPWM_ADC_CVRA |

EPWM 产生的触发信号 A,此信号为所有 CVRA 的 OR 逻辑信号 (n=0/1/2/…/11)。 |

QC 支持的触发信号。 |

EPWM_ADC_CVRB |

EPWM 产生的触发信号 B,此信号为所有 CVRB 的 OR 逻辑信号 (n=0/1/2/…/11)。 |

|

ADC_TRIGE |

外部的触发信号,通过外部管脚输入。 |

|

SW_TRIG |

软件触发信号,通过软件写寄存器字段 TRIGS 产生。 |

-

设置采用合并队列 QC,并设置 15 个采样节点 (Node0~Node14)。

-

对 Q1 的节点寄存器依次配置为 CH0、CH1、CH2 等表示 Node0 - Node11 节点。

-

对 Q2 的节点寄存器依次配置为 CH12、CH13、CH14,表示 Node12~Node14。

-

ADC 在接收到合并队列的有效触发信号后,依次对通道进行一次采样转换,完成后 ADC0 进入空闲状态。

由于合并队列 QC 里设置 15 个采样节点,所以队列中的 Node15~Node23 都不会生效.

ADC0/1 实时队列采样同步

ADC0 和 ADC1 各自拥有实时队列 Q1 和 Q2,用于存储 ADC 转换的结果数据。ADC0 的 Q1 和 Q2 与 ADC1 的 Q1 和 Q2 对应相同的触发信号,这意味着当触发信号到来时,两台 ADC 将同时开始转换过程。通过配置 ADC0 的寄存器字段 ADC_SMP_SYC_EN = 0x1(仅 ADC0 拥有此字段),可以启用 ADC0 和 ADC1 之间的同步功能。

使能同步后,ADC0 的 Q1 与 ADC1 的 Q1 进行同步,同时 ADC0 的 Q2 与 ADC1 的 Q2 也进行同步。两个 ADC 在相同的时间点上对输入信号进行采样和转换,确保数据的一致性和准确性。