存储

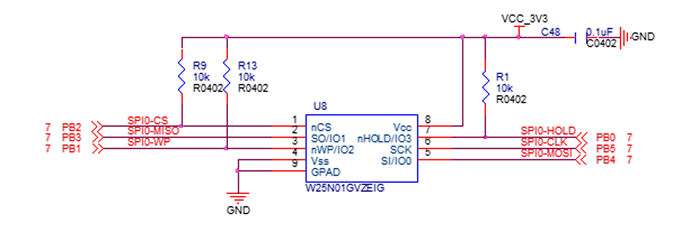

FLASH

SPI0/ 1 为 QSPI 控制器,最大支持四线数据传输,用于 Flash 类型设备的快速读写访问。

- 默认使用 PB0~PB5 引脚的 SPI0 为 Flash 类型设备启动接口。

- QSPI 支持 NAND Flash / NOR Flash,支持单/ 双/ 四线模式。

- IO 最大速率 SDR 100 MHz,仅支持 3.3 V IO 电压,Flash 容量不限制。

注:

- SPI_CS、SPI_WP、SPI_HOLD 必需上拉。

- QSPI 信号除 SPI_CS 外整组必需做等长约束,约束控制在 40 mil 内,否则跑四线模式容易出现速度跑不高的情况。

- 启动阶段 BROM 有 Try 介质过程,PB0~PB5 引脚 SPI0 接口 CS/CMD/CLK 有 ms 级脉冲波形输出,做 IO 输出使用时需注意不要用于敏感电路;若已识别到介质,低优先级的介质不再扫描。

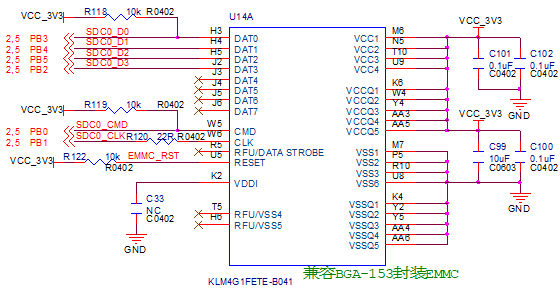

eMMC

使用 SDC0 接口,支持单线/ 四线模式,支持 eMMC 4.41 协议,支持 SDR25/ SDR50/ DDR50 模式。

- IO 最大速率 DDR 50 MHz,仅支持 3.3 V IO 电压。

- D0、CMD 和 RST 信号必需上拉到 VCC33_IO。

注:

- SDC0_D0~SDC0_D3、SDC0_CLK、SDC0_CMD 信号走线做等长约束,约束不大于 40 mil。

- CLK 信号不需上拉,最好在靠近主控端串联 22 欧电阻,若并联容值不超过 22 pF。

- 启动阶段 BROM 有 Try 介质过程,SDC0 接口 D0/CMD/CLK 有 ms 级脉冲波形输出,做 IO 输出使用时需注意不要用于敏感电路;若已识别到介质,低优先级的介质不再扫描。

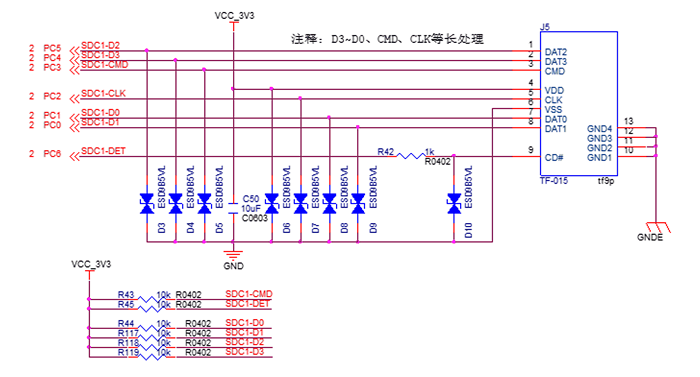

CARD

使用 SDC1 接口,支持单线/四线模式。

- IO 最大速率 DDR 50 MHz,仅支持 3.3 V IO 电压。

- CLK 信号不需上拉,最好在靠近主控端串联 22 欧电阻,若并联容值不超过 22 pF。

- D0、CMD 和 DET 信号建议上拉到 VCC33_IO。

- SD 接口信号线 TVS 管结电容 < 22 pF,否则影响信号传输质量。

- 建议保留 DET 信号线上的 1k 串联电阻,避免在插入 SD CARD 时产生信号下冲,同时提高 GPIO ESD 性能。

注:

- SDC1_D0~SDC1_D3、SDC1_CLK、SDC1_CMD 信号走线做等长约束,约束不大于 50 mil。

- CLK 信号不需上拉,最好在靠近主控端串联 22 欧电阻,若并联容值不超过 22 pF。

- 启动阶段 BROM 有 Try 介质过程,SDC1 接口 D0/CMD/CLK 有 ms 级脉冲波形输出,做 IO 输出使用时需注意不要用于敏感电路;若已识别到介质,低优先级的介质不再扫描。

注:

- 启动优先级:TF-CARD SDC1 > NAND SPI0 > NOR SPI0 > eMMC SDC0。

- 启动阶段 BROM 有 Try 介质过程,PB0~PB5 引脚 SPI0 接口 CS/ MOSI/ CLK 、SDC0/ SDC1 接口 D0/ CMD/ CLK 有 ms 级脉冲波形输出,做 IO 输出使用时需注意不要用于敏感电路;若已识别到介质,低优先级的介质不再扫描输出波形。

- Flash 建议使用 WSON8 带 EPAD 封装,可兼容 NAND/NOR Flash。

- EMMC 建议使用 BGA153 封装,可兼容市面大部分 EMMC,不限制容量,不需要适配驱动 。