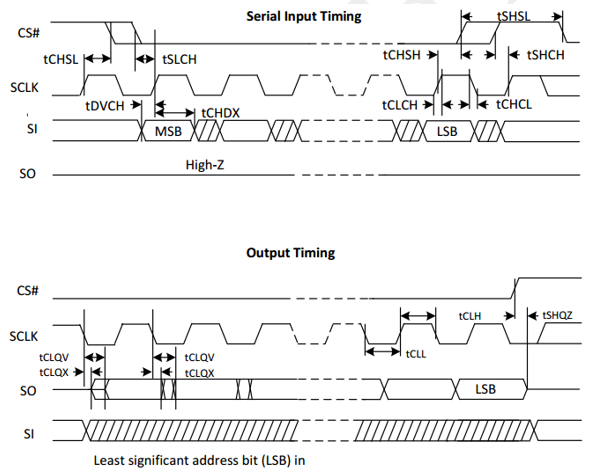

| Input Timing |

| tCLCH |

Serial Clock Rise Time(Slew Rate) |

0.2 |

- |

V/ns |

| tCHCL |

Serial Clock Fall Time(Slew Rate) |

0.2 |

- |

V/ns |

| tCHSL |

CS# Not Active Hold Time |

5 |

- |

ns |

| tSLCH |

CS# Active Setup Time |

5 |

- |

ns |

| tCHSH |

CS# Active Hold Time |

5 |

- |

ns |

| tSHCH |

CS# Not Active Setup Time |

5 |

- |

ns |

| tSHSL |

CS# High Time (read/write) |

20 |

- |

ns |

| tDVCH |

Data In Setup Time |

2 |

- |

ns |

| tCHDX |

Data In Hold Time |

2 |

- |

ns |

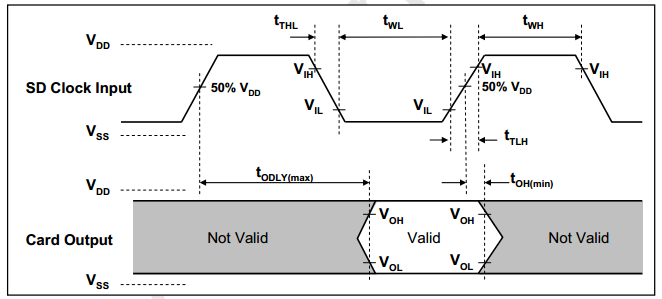

| Output Timing |

| tCLQV |

Clock Low To Output Valid |

|

6.5 |

ns |

| tCLQX |

Output Hold Time |

1 |

- |

ns |

| tCLH |

Serial Clock High Time |

0.45*tck |

- |

ns |

| tCLL |

Serial Clock Low Time |

0.45*tck |

- |

ns |

| tSHQZ |

Output Disable Time |

|

6 |

ns |