功能描述

PHY 接口选择

USB FS OTG 模块使用内部 PHY,且无需使用 UTMI/ULPI 接口,无需配置。

端接电阻配置

-

作 USB Device 模块支持作为 HS 或 LS 设备,先配置 PHY_CTL 寄存器的上拉电阻使能,然后通过 USB_DEV_SPD_SET 可进行速度配置,默认为 FS 设备。这里的配置需要在初始化完成,完成后,即可以实现相应的端接电阻配置。

-

作 USB Host 模块,需配置 PHY_CTL 寄存器的下拉电阻使能。

枚举地址设置

在 USB 的枚举过程,USB Host 会通过 Set Address 命令对 USB Device 的地址进行枚举,枚举地址需在 USB_DEV_ADDR 设置。对于 Host 来说,地址枚举完成后也许在 Channal 寄存器中配置相应的地址。

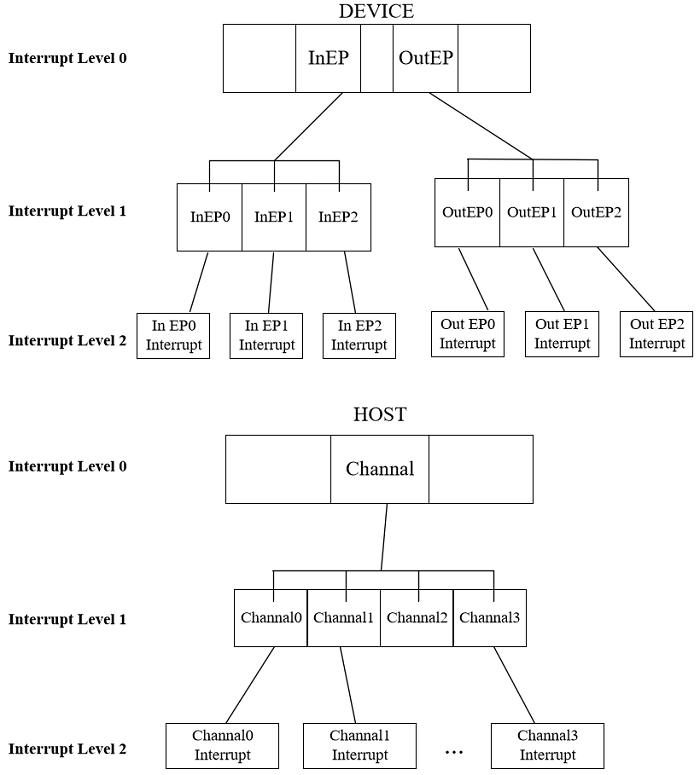

中断

USB Device 模块支持中断:

- 对应的中断会有中断屏蔽控制,默认屏蔽所有中断。

- 在 Interrupt Level 0 的 InEP 和 OutEP 中断,分别为所有 IN 和 OUT

端点的总中断状态。

此位不能写 1 清除,如需清除此位,必须先清除所有端点产生的中断态。

- Interrupt Level 1 是 InEP 和 OutEP

的下一层次逻辑,分别是InEP0/ InEP1/ …/ InEP4 和 OutEP0/

OutEP1/ …/ OutEP4,

InEP0/ InEP1/ …/ InEP15 和 OutEP0/

OutEP1/ …/ OutEP15,InEP0/

InEP1/ …/ InEP8 和 OutEP0/ OutEP1/ …/

OutEP8,表示各个端点的总中断态。默认屏蔽所有端点的中断态,通过屏蔽寄存器来使能某个端点的总中断态。

此层的中断不能写 1 清 0,如需清除此层的中断,必须先清除下一层次的所有中断态。

- Interrupt Level 2 是 IN/ OUT 端点的具体中断态,InEP 在此层次的中断屏蔽控制,共用一套屏蔽控制逻辑,由 INEP_INT_MSK 决定,默认屏蔽所有中断态。OutEP 在此层次的中断屏蔽控制,共用一套屏蔽控制逻辑,由 OUTEP_INT_MSK 决定,默认屏蔽所有中断态。

- 在 Interrupt Level 0 的 InEP 和 OutEP 中断,分别为所有 IN 和 OUT

端点的总中断状态。

- 根据不同应用场景,选择是否使能中断信号。

- IN/ OUT 端点的中断信号存在层次结构的逻辑关系,具体可查看输入输出端点的终端结构图。

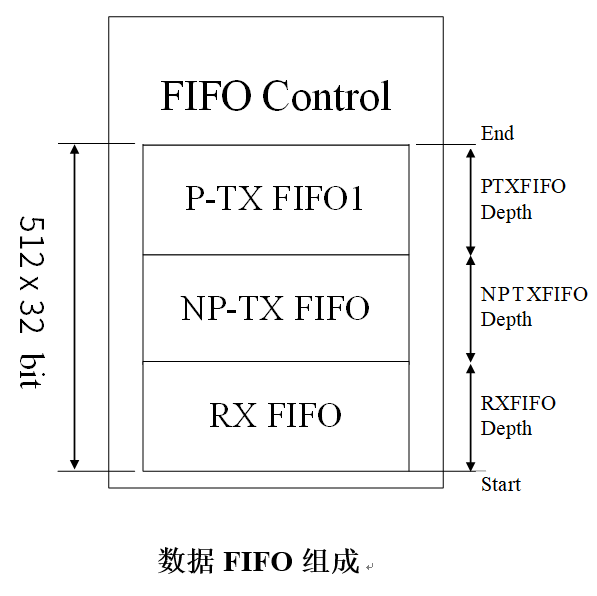

数据 FIFO

USB Device 的数据 FIFO 总深度为 512 x 32 bits。数据 FIFO 组成如下:

- RXFIFO:FIFO 起始位 ,为所有 OUT EP 的共用 FIFO。

- NP-TXFIFO:非周期的 TXFIFO,为所有的 Control/ Bulk 类型的 Device IN EP 或 Host OUT 传输的共用 FIFO。

- P-TXFIFO:周期的 TXFIFO,Interrupt/ Isochronous 类型的 EP 或 Channal 对应 FIFO。无使用到此类型的 EP 或 Channal,可以设置该 FIFO 深度为 0。

通过 FIFO 对应的 FIFO 深度寄存器配置各个 FIFO 的大小,如果不需要,可配置为 0 深度。