功能描述

PSEN

Process Sensor (PSEN),即工艺传感器,特定温度及供电电压情况下,其振荡频率可一定程度上表征芯片的制造工艺偏差。

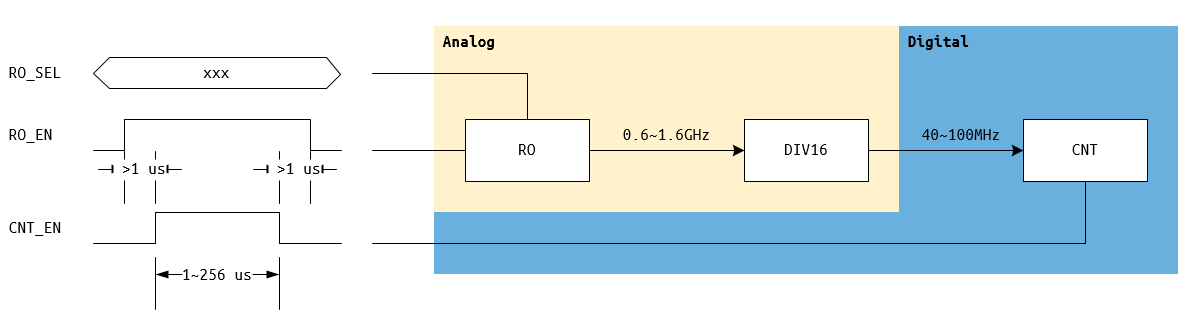

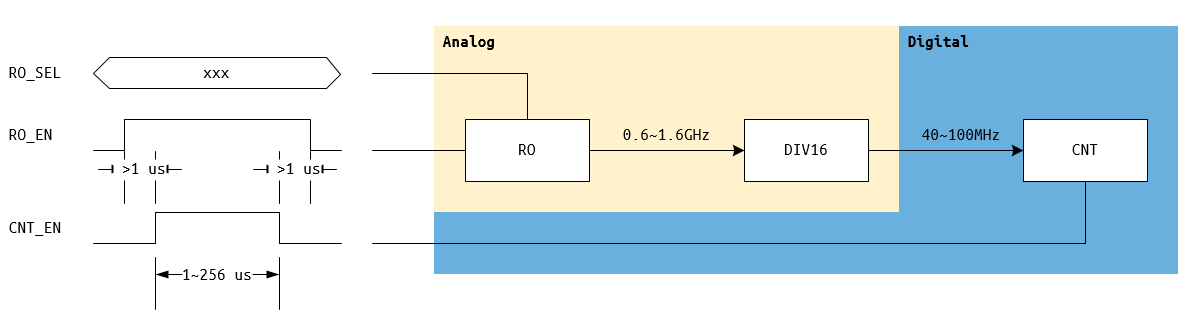

PSEN 工作流程:

图 1. PSEN 工作流程

- 在软件中配置测试参数 (RO_SEL, CNT_TIME) 后,打开测试 (PSEN_EN=1)。

- 打开测试后,PSEN 触发数字电路打开 RO_EN,模拟电路 RO 开始振荡工作,并产生一个经过 16 分频的低频时钟信号供数字电路计数使用。

- 数字电路打开 RO_EN 后延迟打开 CNT_EN。此时 CNT 开始计数,直到预设的 CNT_TIME 时间结束,系统会自动关闭 CNT_EN 并延时关闭 RO_EN,最后将 PSEN_EN 清零表示测试完成。

- 软件检测到 PSEN_EN 清零后,读取 CNT_VAL 值,作为当前 PSEN 的速度。

- 重复此测试可以获取更多 RO 的数据,剔除异常数据取平均,可进一步提高数据的可信度。