编程指南

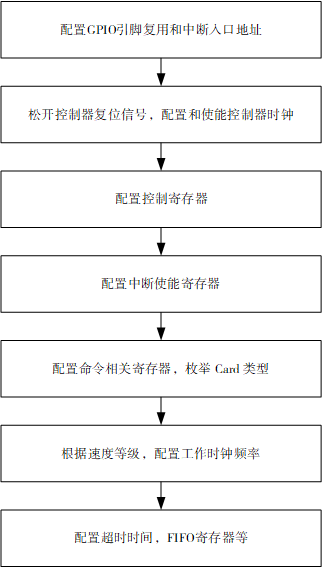

初始化流程

在进行数据传输之前,需要初始化控制器,初始化流程图如下:

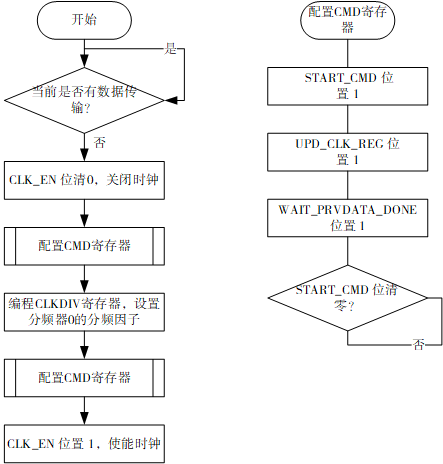

时钟配置流程

建议按照以下流程进行时钟配置:

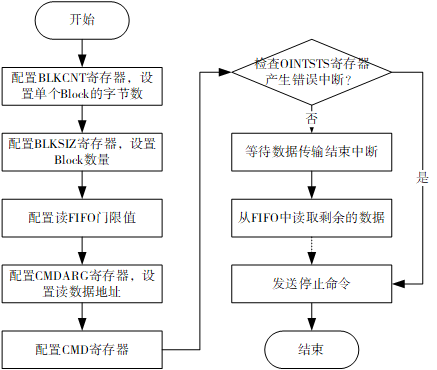

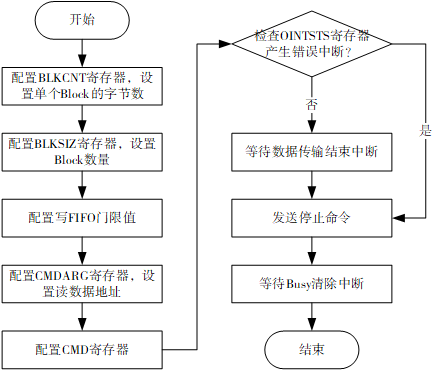

数据传输

读数据流程图

写数据流程图

CMD 寄存器配置表如下:

位域 |

值 |

说明 |

|---|---|---|

START_CMD |

1 |

发送命令完成后自动清零 |

USE_HOLD_REG |

1 或 0 |

基于速度模式选择是否使能保持寄存器 |

UPD_CLK_REG |

- |

非时钟参数刷新命令 |

SEND_INIT |

- |

非初始化序列 |

STOP_ABORT_CMD |

- |

非停止或丢弃命令 |

AUTO_STOP |

0 或 1 |

根据需要选择是否自动发送停止命令 |

TRANS_MODE |

- |

Block 传输 |

TRANS_DIR |

0 或 1 |

|

DATA_EXP |

1 |

数据命令 |

RESP_LEN |

- |

响应长度 |

RESP_EXP |

1 |

命令有响应返回则置 1 |

CMD_INDEX |

命令序列 |

读或写命令序列 |

WAIT_PRVDATA_DONE |

1 |

|

CHECK_RESP_CRC |

1 |

|

软件 Tuning 采样点

Tuning 用于 Host 纠正读数据时的采样点,利用移相器或 Delay Chain 来寻找最佳的采样点,补偿时序偏差。

时序偏差主要由工艺偏差、PCB 走线、电压和温度变化因素引起。

在 DDR50 模式下,即使此时来自 Card 的输出延迟小于一个时钟周期,但是在 Host 控制器内部输入 PAD 的延迟足够大, 使整体的读延时大于一个时钟周期,所以需要进行软件 tuning。

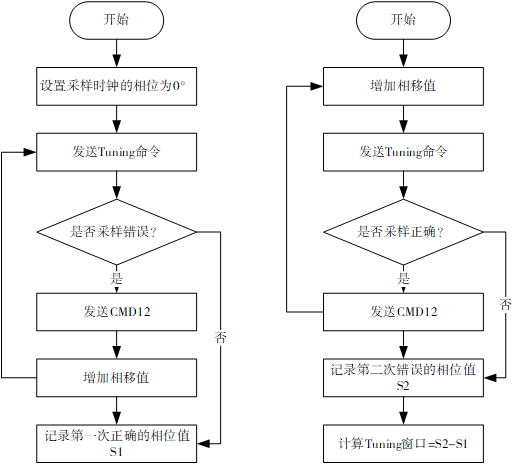

Tuning 最佳采样点,计算 tuning 窗口的流程如下:

DDR 模式编程

对于 eMMC 设备,控制器支持 DDR 模式,支持 4 线 模式。

使用 DDR 模式时需要将时钟控制寄存器的 CLK_DIV 位配置为 0,通过调整采样相位和 Delay Chain 找到最佳的采样点。

此时,时钟频率配置有两种方式:

- 通过 CMU 模块分频配置外部 PLL 输入到 SDMC 模块的时钟,最大支持 32 分频。

- 通过外部时钟输入选择控制寄存器,配置输入到 SDMC 模块的时钟,仅支持 1/ 2/ 4 分频。

DDR 模式 tuning 最佳采样点工作流程如下:

- 初始化 SDMC 控制器和 eMMC,在 SDR 模式下正确读写多个 block 数据。

- 配置 CLK_DIV 位分频系数为 0,配置工作时钟为 50 MHz。

- 配置 eMMC 工作模式为 HS-DDR 模式,控制器总线配置为 DDR 模式。

- 先 tuning 读数据,遍历配置采样相位和 Delay Chain,采样并比较数据,选择窗口最大的一组连续正确的采样点,并计算中间值作为最佳采样点。

- 配置最佳采样点的相位值和 Delay Chain 值,tuning 写操作,选择窗口最大的一组连续正确的驱动值,并计算中间值作为最佳的驱动值。

- 配置最佳的驱动值,再次进行读写测试。