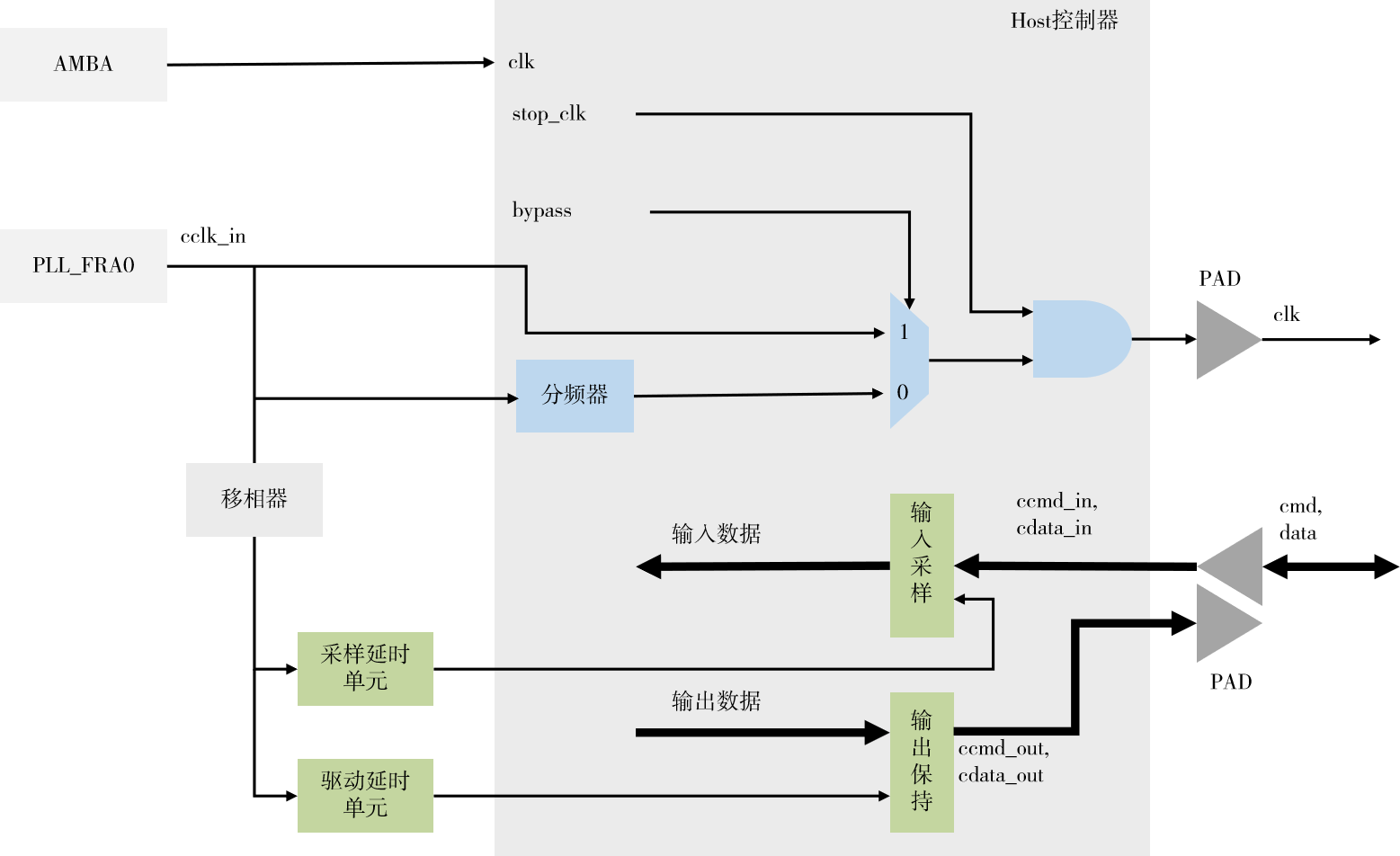

时钟和延时控制

时钟域

控制器内部有多种不同的时钟域,各个时钟域之间的关系描述如下:

- clk:HIF 模块工作时钟和 AHB 总线时钟,所有的配置寄存器使用该时钟。

- cclk_in:输入时钟,CIF 模块大部分模块和寄存器工作在该时钟。

- cclk_in_drv:驱动时钟,输入时钟经过移相器和延迟单元输出的驱动时钟,用于数据和命令的输出驱动。该时钟用来满足不同速度模式下保持时间的要求。

- cclk_in_sample:采样时钟,输入时钟经过移相器和延迟单元输出的采样时钟,用于数据和命令接收采样。

- cclk_out:输出时钟,由 cclk_in 分频后输出给 Device 的工作时钟。

控制器时钟域框图如下:

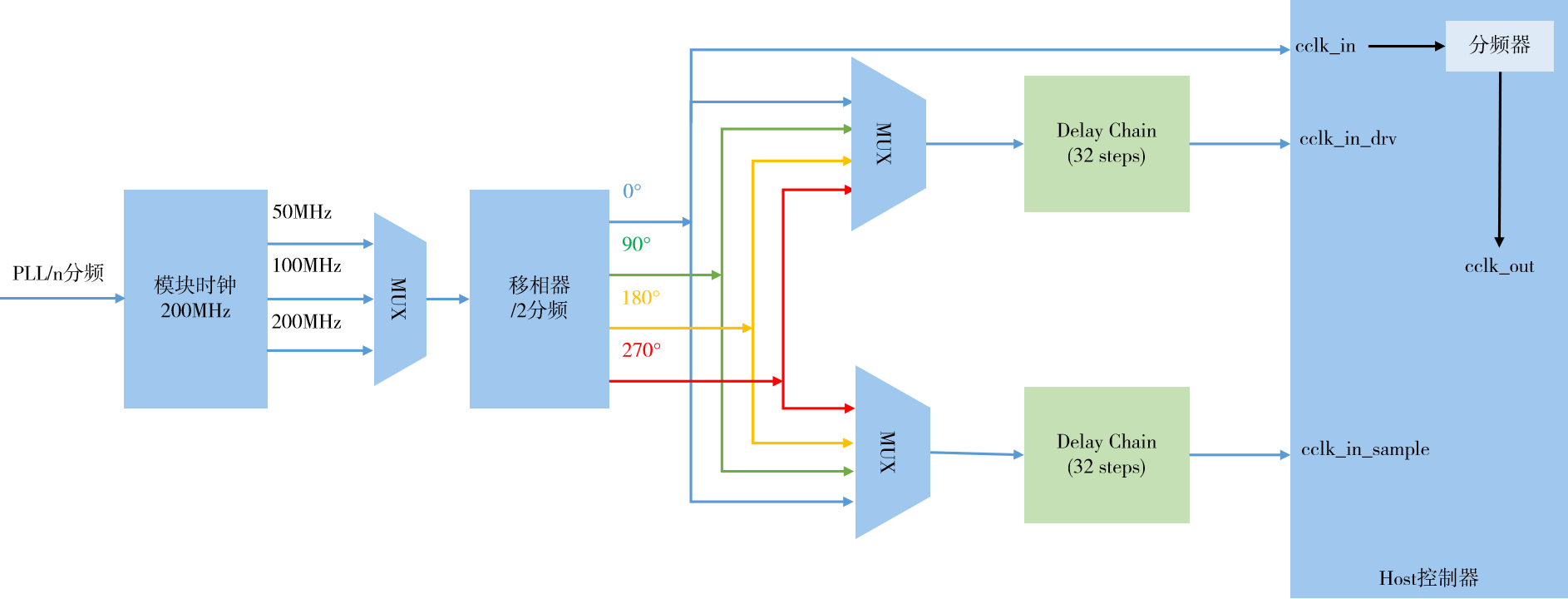

延时控制

由于控制器内部由多种不同的时钟组成,输出驱动时钟和采样时钟需要经过一个相移器和延迟单元进行延迟,以满足不同速度等级的 SD/ MMC 设备稳定的工作时序要求。 因此,需要在 SDMC 控制器外部实现相移和延迟电路。结构框图如下:

延时控制单元的工作流程如下:

- CMU 模块对 PLL 进行分频,输入到 SDMC 控制器的模块时钟频率最大为200 MHz 。

- 配置时钟选择复用器 EXT_CLK_MUX 位域,选择控制器输入时钟。

为满足不同的速度等级要求,共有以下几种模式选择:

- 2b'00:25 MHz,对应速度模式:DS,HS-SDR,HS-DDR

- 2b'01:50 MHz,对应速度模式:HS,HS-SDR,HS-DDR

- 2b'10:100 MHz,对应速度模式:HS-DDR

- DS:SD 卡默认速度模式,工作电平 3.3 V,工作频率 0~25 MHz,最大传输速率 25 Mbps。

- HS:SD 卡高速模式,工作电平 3.3 V,工作频率 0~50 MHz,最大传输速率 50 Mbps。

- HS-SDR:eMMC 高速 SDR 模式,工作电平 3.3 V,工作频率 0~50 MHz,最大传输速率 50 Mbps。

- HS-DDR:eMMC 高速 DDR 模式,工作电平 3.3 V,工作频 率 0~50 MHz,最大传输速率 100 Mbps。

- 经过时钟复用器选择后,时钟进入移相器,通过 2 分频产生四个不同相位的时钟。通过 SDMC_DLYCTRL 寄存器对时钟相位编程选择,共有四种相位可编程:

- 0°,相位与输入时钟相同

- 90°,延时四分之一个时钟周期

- 180°,延时二分之一个时钟周期

- 270°,延时四分之三个时钟周期

- 每个相位之后再经过 Delay Chain 进行 32 级的延迟。Delay Chain 内部由若干个延时单元组成,每个延时单元的延时时间相同。通过 SDMC_DLYCTRL 寄存器对 Delay Chain 进行编程选择。

- 未经过相位延迟和 Delay Chain 的时钟作为控制器的输入时钟 cclk_in。

- 经过控制器内部的分频器分频输出 cclk_out,作为外设的接口时钟。

- 经过内部时钟分频器进行分频 (通过配置 CLK_DIV 位域设置分配系数)后输出符合需求的接口工作时钟。