时钟和电源

电源系统方案

|

方案 |

描述 |

优点 |

缺点 |

|---|---|---|---|

|

1 |

芯片 VCC33_IO(3.3 V)、 VDD11_SYS(1.1 V) 和 LDO18(1.8 V)全都使用外部 DCDC 供电。各路电源平均电流不大于 200mA,选型按 500mA 以上。 |

发热最小、功耗最小 |

成本最高 |

|

2 |

芯片 VCC33_IO(3.3 V)和 VDD11_SYS(1.1 V) 采用外部 DCDC 供电,LDO18 使用内置 LDO 供电。各路电源平均电流不大于 200mA,选型按 500mA 以上。 |

DCDC 电源效率高功耗降低 |

- |

|

3 |

芯片 VCC33_IO(3.3 V/ 300 mA)采用单 3.3 V 供电,VDD11_SYS 和 LDO18 使用内置 LDO 供电。单电源平均电流不大于 300mA,选型按 500mA 以上。 |

电路简洁、成本最低,优先推荐方案 |

LDO 电源效率低、功耗最高 |

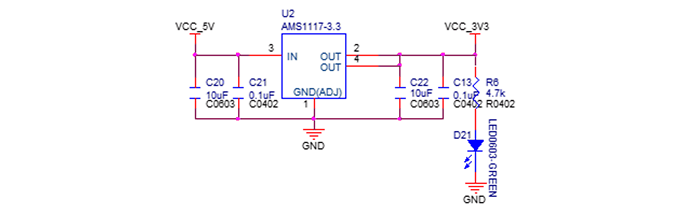

POWER

-

内置 LDO18,芯片复位时默认关闭,SDK 可在 pbp_cfg.json 文件中配置打开或关闭,输出 1.8 V~1.92 V 供 PSRAM 使用,LDO18 引脚外部接 10 uF + 0.1 uF 旁路电容即可。

-

内置 LDO1x,芯片复位时默认开启,SDK 可在 menuconfig 中配置打开或关闭,输出 1.1 V~1.21V 供 VDD11_SYS 使用,VDD11_SYS 引脚外挂 10 uF + 0.1 uF 旁路电容即可。

-

内置 LDO25,默认开启,供内部模拟模块使用,LDO25 引脚外部接 1 uf 旁路电容即可。

-

若使用内置 LDO18 和 LDO1x,只有 3.3V 单独供电,因转换效率问题,功耗会较外置 DCDC 增加 100mW 左右。

- 一路 DCDC 电源方案,7 寸屏动态场景开发板,芯片表面温度 40 左右,芯片功耗约 280 mW ,芯片休眠功耗约 6 mW 。

- 若使用外部 1.8 V 和 1.1 V 供电,内置 LDO18 和 LDO1x 需要软件关闭。

- 无上下电顺序要求,VCC33_IO 上电上升沿时间需大于 100 us 而小于 5 ms。

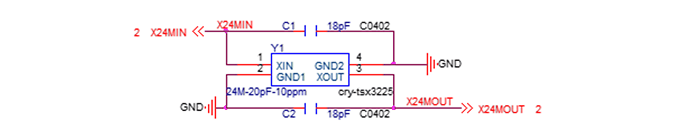

PLL

- D123外挂 24 MHz 晶振精度要求小于 ± 20 ppm,匹配电容根据晶体负载电容选择。

- PLL_XO 建议串联 0R 电阻,便于调试振荡幅度。

- D121 内置 24M OSC,精度< 2%,不支持外挂晶振

BOOT

如何进入烧录模式:

- 存储介质空片情况下,可直接进烧录模式,此时 PA0/PA1 UART0 引脚会打印字符 A 说明进了烧录模式。或使用 PA0/PA1 UART0 连接电脑 Aiburn 烧录工具能识别烧录。

- 存储介质空片或者有固件情况,SDC1 TF-CARD 能在上电或复位时使用 1 数据线或 4 数据线强制进行烧录 ,通常用于量产及升级。

- 存储介质有固件情况下,SDK 默认使用 PA0 当做 BOOT 检测引脚,上电或复位时 BOOT 下拉低电平进入烧录模式 。

如何修改 BOOT 引脚配置:

- 在 pbp_cfg.json 文件配置,路径

target/product/xxx/pack/pbp_cfg.json

其中 product 为具体型号名称,如 D12x,D13x 或 G73x。

比如将 boot 引脚改为使用 PE12,改动说明如下:

upgmode_pin_cfg_reg :“0x187004b0” ,//PE12, 0x18700000+0x80+G*0x100+P*0x4

upgmode_pin_cfg_val : “0x10321”,//pinmux val, 默认不变

upgmode_pin_input_reg :“0x18700400” , //input val, 0x18700000+G*0x100

upgmode_pin_input_msk :“0x1000” , //bit mask,二进制第 12 位,转 16 进制即 0x1000

upgmode_pin_input_val :“0x0”, //bit val,0 为低电平检测,若是高电平,改为 0x1000 按位检测

upgmode_pin_pullup_dly :“500” ,//检测 delay,默认不变RESET

RESETN 引脚内置约 30 ㏀ 上拉电阻和去抖滤波,低电平复位,不使用可直接悬空,建议预留按键或跳线方便调试。

- 上电 VCC33-IO 高于 2.5V 后延迟 7ms 左右放开复位,下电 VCC33 低于 1.7V 彻底复位,RESET 下拉大于 2ms 后复位。

- 若想延迟放开复位,可外挂电容,最大建议不超过 4.7uF 。

- 可使用电压监控、外部看门狗、外部 IO 进行复位控制 。