配置参数

RGB

-

mode:RGB 模式,当前 AiPQ 工具仅支持并行 RGB 模式,

-

format:RGB 显示接口的输出格式。

format

interface-format

备注

24BIT

PRGB_24BIT

RGB888 24 个数据 pin 输出

18BIT_LD

PRGB_16BIT_LD

Lowest Discarded, 将 24 个 pin 中最低 6 个 pin 丢弃

18BIT_HD

PRGB_16BIT_LD

Highest Discarded, 将 24 个 pin 中最高 6 个 pin 丢弃

16BIT_LD

PRGB_16BIT_LD

Lowest Discarded, 将 24 个 pin 中最低 8 个 pin 丢弃

16BIT_HD

PRGB_16BIT_LD

Highest Discarded, 将 24 个 pin 中最高 6 个 pin 丢弃

PRGB 的 18bit/16bit 提供 2 种输出模式,可根据不同的封装或走线需求进行选择。

- clock-phase:pixel 时钟输出相位选择,允许时钟上升沿延后数据 0°/90°/180°/270°

相位。时钟延后 90°相位会修改时钟极性。

clock phase

macro

备注

0

DEGREE_0

时钟上升沿延后数据 0° 相位

90

DEGREE_90

时钟上升沿延后数据 90° 相位

180

DEGREE_180

时钟上升沿延后数据 180° 相位

270

DEGREE_270

时钟上升沿延后数据 270° 相位

- data-mirror:RGB 数据组内大小端输出。默认输出低位到高位 0 - 7,使能则变为 7 - 0 输出。

- pinmux 配置:详情可查看Pinmux 配置 中关于 RGB 的详细描述。

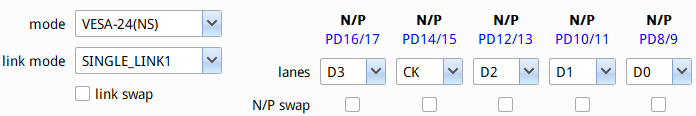

LVDS

-

mode:LVDS 模式设置,支持

vesa-24,jeida-24,jeida-18等接口标准LVDS Mode

data-mapping

备注

VESA-24(NS)

vesa-24

String 类型参数

JEIDA-24

jeida-24

String 类型参数

JEIDA-18

jeida-18

String 类型参数

-

link-mode:LVDS Link 模式设置

LVDS Link mode

data-channel

备注

SINGLE_LINK0

single-link0

单 link 输出,输出选择 link0 通道

SINGLE_LINK1

single-link0

单 link 输出,输出选择 link1 通道

DOUBLE_SCREEN

double-screen

单 link 输出,link0 和 link1 同时输出,可驱动双屏同显

DUAL_LINK

dual-link

dual link 输出,奇偶像素同时输出

-

link swap:LVDS Link0 与 Link1 整组交换。使能 Link swap 后,Link1 的 pin 脚输出 Link0 的数据,Link0 的 pin 脚输出 link1 的数据。

-

lanes:控制 LVDS Link 内部 5 个通道的差分信号输出,允许 5 对差分信号任意互换。

5 对差分信号分别为 D3 CK D2 D1 D0。

-

N/P swap:LVDS Link 差分信号的极性控制,默认正相。

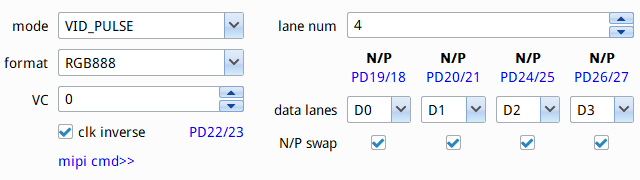

MIPI-DSI

-

mode:DSI 模式设置

DSI mode

panel_dsi

备注

VID_PULSE

DSI_MOD_VID_PULSE

video pulse mode

VID_EVENT

DSI_MOD_VID_EVENT

video event mode

VID_BURST

DSI_MOD_VID_BURST

video burst mode

CMD_MODE

DSI_MOD_CMD_MODE

command mode

-

format:DSI 显示接口输出格式

DSI format

panel_dsi

备注

RGB888

DSI_FMT_RGB888

rgb888

RGB666L

DSI_FMT_RGB666l

rgb666 packed

RGB666

DSI_FMT_RGB666

rgb666

RGB565

DSI_FMT_RGB565

rgb565

-

lane_num:数据通路数量,支持 1 ~ 4 组差分数据通路。

-

data lanes:数据通道输出控制,允许数据通道任意互换,时钟通道不支持交换。

-

N/P swap:DSI 数据通路极性控制,默认正相。

-

clk inverse:DSI 时钟通路极性控制,默认正相。

-

VC:DSI 虚拟通道 ID,Virtual Channel Identifier。

-

MIPI-DSI command:AiPQ 工具支持添加 MIPI-DSI 屏幕的初始化 command,允许从 txt 文件导入,或者直接在 MIPI 命令窗口编辑。

command 语法:header data命令以行为单位,每行以特定的标志开头,允许空行,支持数据换行,数据标志头**大小写敏感**,格式如下所示:

-

mipi.dcs

-

mipi.generic

-

delay

delay 以毫秒为单位进行延时。mipi.generic 0xF0,0xC3 mipi.generic 0xE4,0x40,0x0F,0x2F mipi.dcs 0x11 delay 120 mipi.dcs 0x29

-

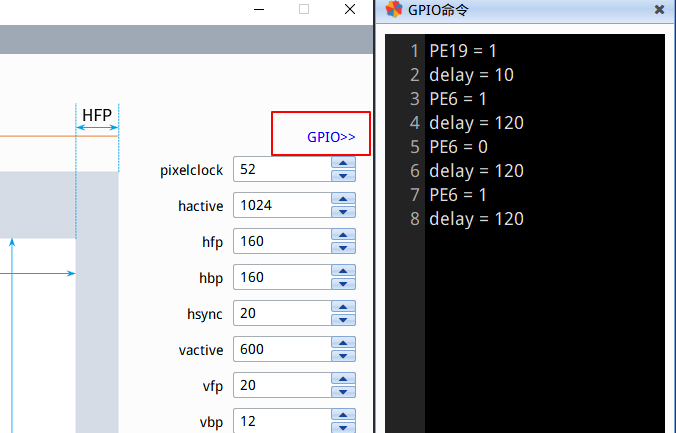

GPIO

调屏功能支持控制 GPIO 引脚,用于测试 LCD 外设的

backlight, reset, power

等引脚。

在 GPIO 命令编辑窗口写入 GPIO 操作指令,PE19 控制背光,PE6 控制 reset,点击 写入配置 使

GPIO 操作生效。

GPIO 操作指令格式如下,其大小写敏感:

-

PXn:

- P: 标记头

- X: GPIO 组编号

- n: GPIO 组内编号。

例如, PF19 表示 F 组第 19 引脚。

-

delay:以毫秒为单位进行延时

-

0/1:指定输出高低电平

GPIO 操作为最高优先级,引脚会强制设为通用 GPIO,并输出指定电平。

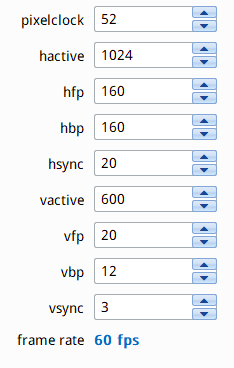

时序参数

-

pixelclock:单位为

MHz,计算公式为:pixelclk=(hactive + hfp + hbp + hsync) * (vactive + vfp + vbp + vsync) * fps注:点击

写入配置 按钮使新参数生效,AiPQ 工具会自动计算帧率 (fps)。

按钮使新参数生效,AiPQ 工具会自动计算帧率 (fps)。

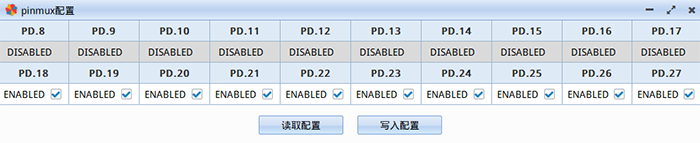

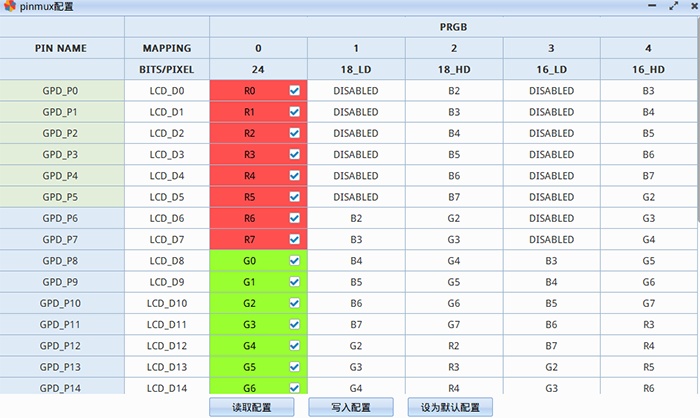

Pinmux 配置

ArtInChip SoC 产品接口丰富,pinmux 配置页面能为 RGB 屏幕的 pin 脚连接提供参考,帮助工程师更高效地阅读开发板原理图。

pinmux 配置页面允许 enable/disable 引脚的 lcd 数据输出,支持简单的 lcd pin 调试。

- RGB pinmux 配置页面如下所示:

提示:

提示:部分 RGB888 屏幕在实际使用上呈现 RGB666 的效果,可通过禁用 RGB 三组 pin 脚的低位进行测试。

-

LVDS pinmux 配置页面支持检查 pin 脚是否被配制成 LVDS func,并允许 enable/disable 引脚的 LVDS 数据输出,支持简单的 pin 调试。

MIPI-DSI pinmux 配置页面支持检查 pin 脚是否被配制成 MIPI-DSI func,并允许 enable/disable 引脚的 MIPI-DSI 数据输出,支持简单的 pin 调试。