功能描述

计数器功能模块

计数时钟

计数器的时钟 EPWM_CNT_CLK 由 SYS_CLK 进行分频得出:

- Divisor1/2 为寄存器 EPWM_CLK_DIV1/2。

- 除数 Divisor1 的可配置范围为 1/ 2/ 4/ 6/ 8/ 10/ 12/ 14。

- 除数 Divisor2 的可配置范围为 1/ 2/ 4/ 8/ 16/ 32/ 64/ 128。

- 开启 EPWM 计数器的计数,需使能全局的控制信号 EPWM_CNT_GLB_EN。

计数方式

- 递增计数:计数器从 0 开始递增计数,计数至 EPWM_CNT_PRDV 值时,完成一个周期的计数,并且复位至 0

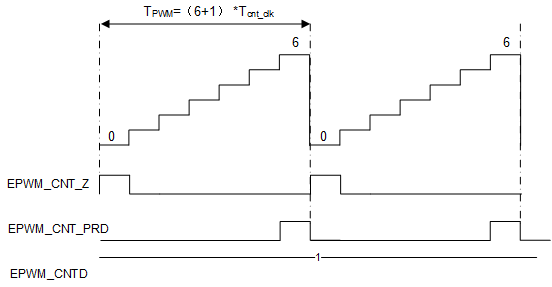

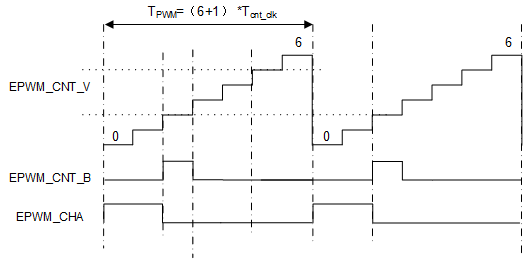

重新开始计数。计数器递增计数图示 中,设置 EPWM_CNT_PRDV = 6 的递增计数,此时开始从 0 到 6 的递增计数:

- 在计数值为 0 时,信号 EPWM_CNT_Z = 1

- 在计数值为EPWM_CNT_PRDV 的时候,信号EPWM_CNT_PRD = 1

- 而指示计数方向的信号EPWM_CNTD 一直为高电平,指示为递增计数。

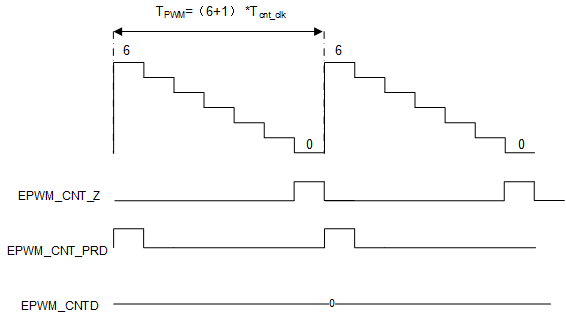

图 1. 计数器递增计数图示 - 递减计数:计数器从 EPWM_CNT_PRDV 开始递减计数,计数至 0 时,完成一个周期的计数,并且复位至 EPWM_CNT_PRDV 重新开始计数。计数器递减计数图示中,设置 EPWM_CNT_PRDV = 6 的递减计数,此时进行从 6 到 0 递减计数:

- 在计数值为 0 的时候,信号 EPWM_CNT_Z = 1。

- 在计数值为 EPWM_CNT_PRDV 的时候,信号 EPWM_CNT_PRD = 1。

- 指示计数方向的信号 EPWM_CNTD 一直为低电平,指示为递减计数。

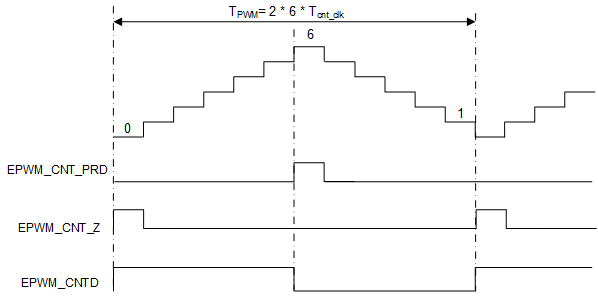

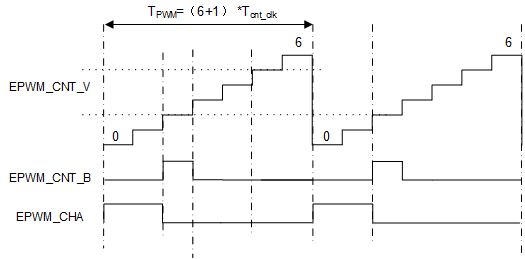

图 2. 计数器递减计数图示 - 先递增后递减计数:计数器从 0 开始递增计数,计数至 EPWM_CNT_PRDV 后进行递减计数,当计数器计数为

1,完成一个周期的计数。下一个周期继续从 0 开始进行先递增后递减计数。计数器先递增后递减计数示例中,设置 EPWM_CNT_PRDV = 6 的先递增再递减计数,此时进行先从 0 到 6 的递增计数再从 6 到 0 的递减计数:

- 在计数值为 0 的时候,信号 EPWM_CNT_Z = 1。

- 在计数值为 EPWM_CNT_PRDV 的时候,信号 EPWM_CNT_PRD = 1。

- 指示计数方向的信号 EPWM_CNTD 在前半周期为高电平指示此时为递增计数,后半周期指示为递减计数。

图 3. 计数器先递增后递减计数示例

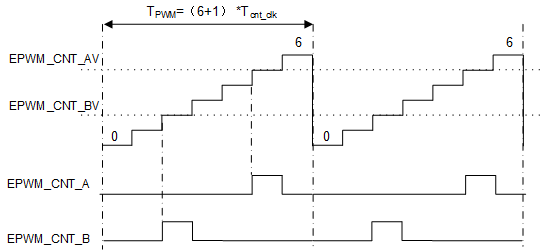

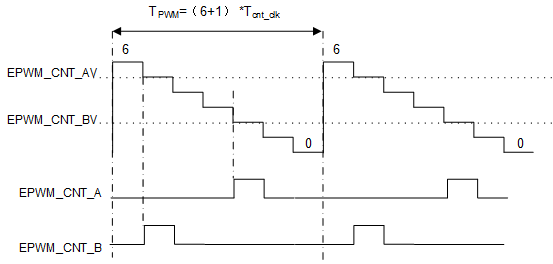

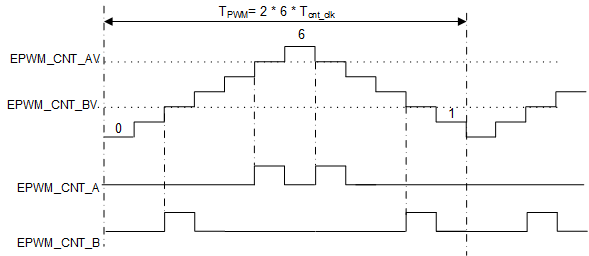

计数比较

在计数数值达到预设的设定值时,即达到 EPWM_CNT_AV 与 EPWM_CNT_BV 时,计数器可以产生相应的信号 EPWM_CNT_A 与 EPWM_CNT_B。

- 若为递增计数至 EPWM_CNT_AV 产生的信号,记为 EPWM_CNT_UA。

- 若为递减计数至 EPWM_CNT_AV 产生的信号,记为 EPWM_CNT_DA。

- 若为递增计数至 EPWM_CNT_BV 产生的信号,记为 EPWM_CNT_UB。

- 若为递减计数至 EPWM_CNT_BV 产生的信号,记为 EPWM_CNT_DB。

产生的信号输出至 EPWM 生成模块以及 Trigger & Interrupt 模块使用。具体时序图如下:

计数同步

计数器具有同步的功能,同步信号的使能后,可以使得计数器计数值跳至 EPWM_CNT_PHV 计数同步相位寄存器的数值。

- IN_SYNC,对于 EPWM 子模块,是外部输入信号,上升沿有效,各个 EPWM 子模块的 IN_SYNC 的信号来源可参考同步信号网络示例。

- SW_SYNC,为 EPWM 模块通过寄存器设置 EPWM_SW_FRC_SYNC 位而产生,即由软件控制产生。

- IN_SYNC 与 SW_SYNC 的信号经过或逻辑后,决定计数器的同步。

计数器还会产生输出的同步信号 OUT_SYNC,通过寄存器设置可以选择不同的信号作为 OUT_SYNC。同步输出信号源 中展示了 OUT_SYNC 的来源。

- 的输出同步信号通过 GPIO_MUX 输出给外部器件,并且进行脉冲的 8*SYS_CLK 的长度延长。

- CPM0_COH 以及 CPM1_COH 分别为 CPM0 和 CPM1 输出的比较信号。

寄存器更新

寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 支持以下更新模式,且各有独立控制的更新模式的控制位。

- 立即更新模式:

- 对寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 的数值写入,会立即生效,从而影响当前的 EPWM 生成。

- 可能出现在当前的周期,新写入的数值与计数器的数值错过比较时刻,导致 AV 和 BV 的动作未发生,进而造成当前周期的输出 EPWM 占空比异常,例如 100% 或 0% 占空比。

- 通过寄存器字段 EPWM_CMPA_IMD_UPDT_PULSE_EN、EPWM_CMPB_IMD_UPDT_PULSE_EN = 1,可以避免立即更新带来的错误 EPWM 输出。

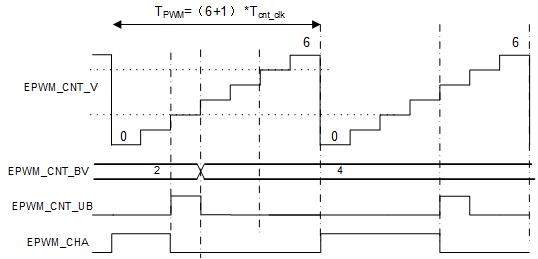

- 影子寄存器更新模式:

- 对寄存器 EPWM_CNT_PRDV、EPWM_CNT_AV 以及 EPWM_CNT_BV 的数值的写入,暂时存入各自的影子寄存器,不会立即生效,只有当计数器计数值到指定加载点时才进行更新,影子寄存器的数值生效。

- EPWM_CNT_BV 影子寄存器更新示例中,当对 EPWM_CNT_BV 的数值进行写操作,将数值从 0x2 改变为 0x4 后,并没有立即生效,而是在计数值复位至 0 开始下一个周期的计数后,EPWM_CNT_BV 的数值才生效,从而改变了 EPWM 信号的占空比。

图 9. EPWM_CNT_BV 影子寄存器更新示例

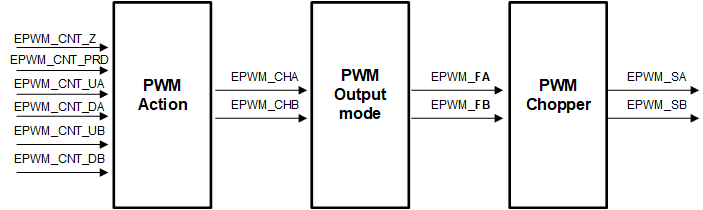

EPWM 生成模块

- 下列信号产生的动作:

- EPWM_CNT_Z

- EPWM_CNT_PRD

- EPWM_CNT_UAV

- EPWM_CNT_DAV

- EPWM_CNT_UBV

- EPWM_CNT_DBV

- 寄存器中 EPWM 的输出模式。

- EPWM 动作控制模块:触发产生 EPWM 动作的信号,为计数器功能模块产生的信号。

- EPWM 输出模式:可以根据如下寄存器配置 EPWM 的输出。

- EPWM_CH_SEL[1:0]

- EPWM_POL_SET[1:0]

- EPWM_BP_SET[1:0]

- EPWM Chopper 模块

EPWM 动作控制模块

EPWM 动作控制模块,触发产生 EPWM 动作的信号为计数器功能模块产生的信号。所有的信号对 A、B 通道均有效。各信号描述如下:

- EPWM_CNT_Z,计数器数值达到 0 时产生。

- EPWM_CNT_PRD ,计数器数值达到 EPWM_CNT_PRDV 时产生。

- EPWM_CNT_UA,计数器递增计数达到 EPWM_CNT_AV 时产生。

- EPWM_CNT_DA,计数器递减计数达到 EPWM_CNT_AV 时产生。

- EPWM_CNT_UB,计数器递增计数达到 EPWM_CNT_BV 时产生。

- EPWM_CNT_DB,计数器递减计数达到 EPWM_CNT_BV 时产生。

当优先级高的信号所触发的动作为无动作时,控制器跳过该信号控制,由其它优先级的信号控制,如在 EPWM_CNT_UB/ DB 所触发的动作为无动作时,控制器则跳过 CMPB 的动作控制,进行 EPWM_CNT_UA/DA 的动作控制。各信号触发的动作优先级见动作控制信号优先级。

通过配置寄存器 EPWMA_ACT 和 EPWMB_ACT,可以在各信号上执行以下动作类型:

- 置 1:EPWM 输出信号设置为高电平。

- 置 0:EPWM 输出信号设置为低电平。

- 翻转:EPWM 输出信号进行翻转,若当前信号为高,动作执行将 EPWM 信号设置为低电平。

- 无操作:EPWM 输出信号无变化,维持现有的信号。

举例说明:假设 EPWM_CHA 动作满足以下条件,可以得出 EPWM_CHA 信号生成示例:

- 计数器递增计数,EPWM_CNT_BV = 0x2,EPWM_CNT_PRD = 0x6

- EPWM_CHA 的动作设定:

- EPWMA_ACT_CNTZ = 0x2:置 1

- EPWMA_ACT_CNTUBV = 0x1:置 0

- 其它的动作设定则为无动作

EPWM_CHA 信号生成示例中,生成的占空比则为 2/7 ≈ 28.5%

图 11. EPWM_CHA 信号生成示例

软件强制控制信号

- 非持续的软件强制控制信号:信号非持续。若有下一个动作控制信号出现,则由下个控制信号控制 EPWM 的动作。

- 持续的软件强制控制信号:信号持续。即使下一个动作控制信号出现,由于软件强制控制信号优先级最高且信号持续,所以屏蔽后续的控制信号,仍然由持续的软件强制控制信号控制

EPWM 的动作。

- 控制 EPWM 动作的类型,包括置 1 和置 0 (寄存器 0x002C EPWM_ACT_SW_CT)。

- 如需由其它信号控制 EPWM 的动作,则关闭此功能。

动作控制信号优先级

动作控制信号中,软件强制控制信号的优先级始终最高,其它信号的优先级在不同的计数模式下,排列会有所差异,动作控制信号优先级具体如下。当同时出现多个动作控制信号时,按照优先级最高的控制信号执行机制。

递增计数模式,优先级排列:

优先级 |

递增阶段 |

|---|---|

1(最高) |

软件强制控制信号 |

2 |

EPWM_CNT_UB/ EPWM_CNT_DB |

3 |

EPWM_CNT_UA/ EPWM_CNT_DA |

4 |

EPWM_CNT_PRD |

5(最低) |

EPWM_CNT_Z |

EPWM 输出模式

-

EPWM_CH_SEL[1:0],通道选择控制信号,分别选择上升沿信号处理通道的输入源,以及下降沿信号处理通道的输入源。两路的信号处理通道都可以选择 CHA 或 CHB。注:通过对上升沿信号以及下降沿信号可以实现死区控制,具体配置可查看 EPWM 死区控制。

-

EPWM_POL_SET[1:0],极性选择控制信号,选择正极性或负极性的信号。

-

EPWM_BP_SET[1:0],旁通选择,EPWM_BP_SET[0]可以选择旁通 EPWM_CHA,EPWM_BP_SET[1] 可以选择旁通 EPWM_CHB。

EPWM 死区控制

- EPWM_RE_DZCTL

- EPWM_FE_DZCTL

EPWM_CHA 插入上升沿死区以及下降沿死区中,以通道 EPWM_CHA 的信号为例,分别设置 EPWM_RE_DZCTL = EPWM_FE_DZCTL = 1,得到如下的信号,实现上升沿/ 下降沿的死区时间控制为 1 * Tcnt_clk。

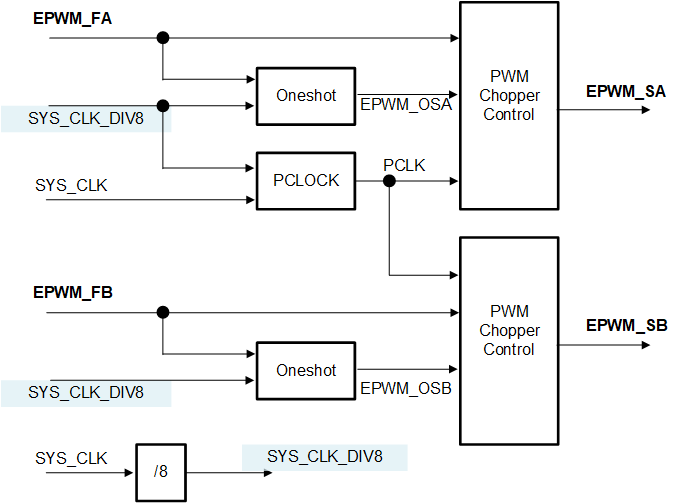

EPWM Chopper 模块

- 寄存器 EPWM_CHOP_EN = 0x0:EPWM Chopper 模块旁通

- 寄存器 EPWM_CHOP_EN = 0x1:EPWM Chopper 模块工作

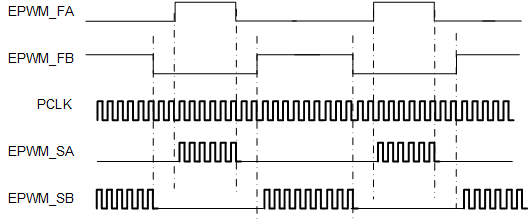

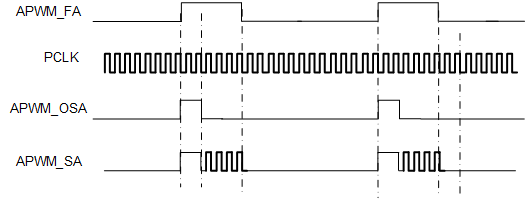

- Oneshot 信号以 EPWM_FA/FB 信号的上升边沿为触发边沿,产生脉宽为 EPWM_CHOP_OS_WTH * PSCLK 的 Oneshot 信号。

PCLK 以及 Oneshot 调制图示 中,EPWM_CHOP_OS_WTH = 0x1,产生了 EPWM_OSA 信号,利用 EPWM_OSA 以及 PCLK 信号进行调制,得出 EPWM_SA。

- PCLOCK 对 EPWM_FA 和 EPWM_FB 信号进行调制,生成 PCLK

信号。PClock 模块控制产生的 PCLK 信号的频率以及占空比。

- 寄存器 EPWM_CHOP_FRE:配置分频系数

- 寄存器 EPWM_CHOP_DUTY:调节和配置占空比,调节范围是 12.5%~87.5%,每档位 12.5%。

PCLK 调制 EPWM 信号中以互补的死区控制的一对信号,进行了 PCLK 信号的调制。

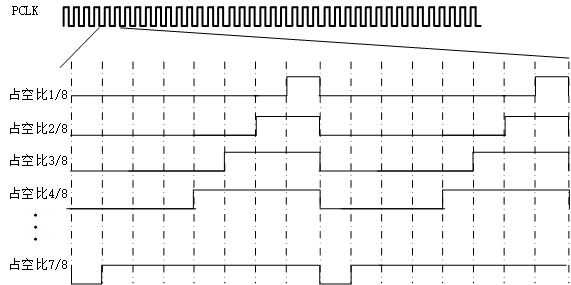

图 15. PCLK 调制 EPWM 信号 PCLK 的占空比调整则如PCLK 的占空比所示。

图 16. PCLK 的占空比 - EPWM Chopper Control 利用 EPWM_OSA/ OSB 和 PCLK

信号输出调制信号 EPWM_SA 和 EPWM_SB。

图 17. PCLK 以及 Oneshot 调制图示

EPWM 保护模块

EPWM 初始值配置

通过寄存器可以配置 EPWM 的输出信号EPWM0/1/.../11_A 以及 EPWM0/1/.../11_B 在 EPWM 功能未使能的情况下的初始值。

- 若 EPWM_A_INIT = 0x0,EPWM 模块未使能,EPWM0_A 输出低电平。

- 若 EPWM_A_INIT = 0x1,EPWM 模块未使能,EPWM0_A 输出高电平。

- 若 EPWM_A_INIT = 0x2/3,EPWM 模块未使能,EPWM0_A 输出为高阻态。

故障模式

-

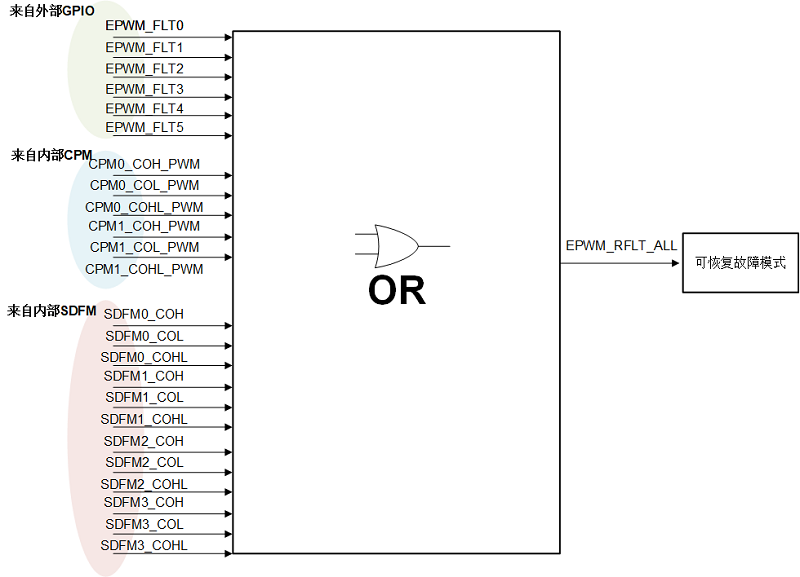

可恢复故障模式:

- 当 EPWM_RFLT_ALL 有效,EPWM 模块立即执行故障操作,如果有使能中断模式,则产生 EPWM_RC_FALT_INT 中断。

- 当计数器计数复位至 0,若 EPWM_RFLT_ALL 信号变回无效状态,EPWM 的故障操作解除,EPWM 可以继续正常工作。

-

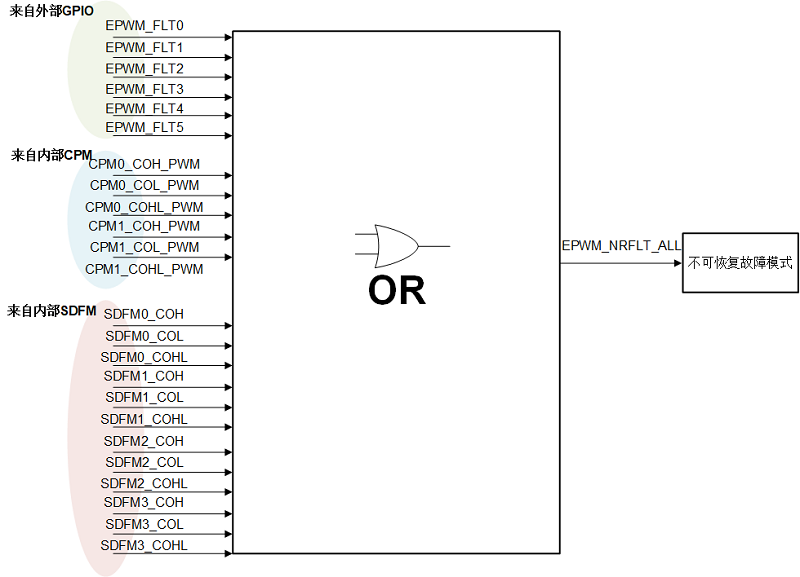

不可恢复故障模式:

- 当 EPWM_NRFLT_ALL 有效,EPWM 模块立即执行故障操作,如果有使能中断模式,则产生 EPWM_NRC_FALT_INT 中断。

- 当出现不可恢复的故障时,EPWM

一直处于故障操作的状态,不能修改。

不可恢复故障的消除,只能通过软件写寄存器消除此状态,才可以使得 EPWM 再次正常工作。。

故障指示输入

- 可恢复故障指示输入

图 18. EPWM 可恢复故障指示输入 - 不可恢复故障指示输入:

图 19. EPWM 不可恢复故障指示输入

故障操作

-

EPWM 强制输出高电平

-

EPWM 强制输出低电平

-

EPWM 强制输出高阻态

-

无操作

故障中断

故障中断,由可恢复故障中断 EPWM_RC_FALT_INT 与不可恢复中断 EPWM_NRC_FALT_INT 进行或逻辑所得 EPWM_FALT_INT 信号。

ADC 采样触发和中断模块

ADC 采样触发

- 每个 EPWM 模块可以最多产生 2x ADC 采样触发信号,即输出 EPWMn_ADC_CVRA 和 EPWMn_ADC_CVRB。

- EPWMn_ADC_CVRA 和 EPWMn_ADC_CVRB 分别经过 OR

逻辑后,对应生成 EPWM_ADC_CVRA 和 EPWM_ADC_CVRB,送到

ADC0/1,再分别作为 ADC0/1 的队列 1 和队列 2 的触发信号。

图 20. ADC 采样触发图示 - 产生采样触发信号的输入源与控制 EPWM 动作的信号一致,可以选择以下信号作为触发信号:注:CPM 所有输出的信号的上升沿才是触发信号。

-

EPWM_CNT_Z

-

EPWM_CNT_PRD

-

EPWM_CNT_UA

-

EPWM_CNT_DA

-

EPWM_CNT_UB

-

EPWM_CNT_DB

-

CPM0_COH

-

CPM0_COL

-

CPM0_COHL

-

CPM1_COH

-

CPM1_COL

-

CPM1_COHL

-

-

通过寄存器字段 EPWM_ADC_CVRA/ B_DIV 可以配置 ADC 采样触发信号产生的频次。

频次可配置为每次、每两次、每三次产生触发信号。以 CNT_Z 信号为例,若配置频次为每三次,当出现三次 CNT_Z 有效信号,会产生一次 ADC 采样信号。

EPWM 中断

- EPWM_CNT_Z

- EPWM_CNT_PRD

- EPWM_CNT_UA

- EPWM_CNT_DA

- EPWM_CNT_UB

- EPWM_CNT_DB

通过寄存器字段 EPWM_INT_DIV 可以配置 中断信号产生的频次。

频次可配置为每次、每两次、每三次产生触发信号。以 CNT_Z 信号为例,若配置频次为每三次,当出现三次的 CNT_Z 有效信号,会产生一次 EPWM 中断信号。

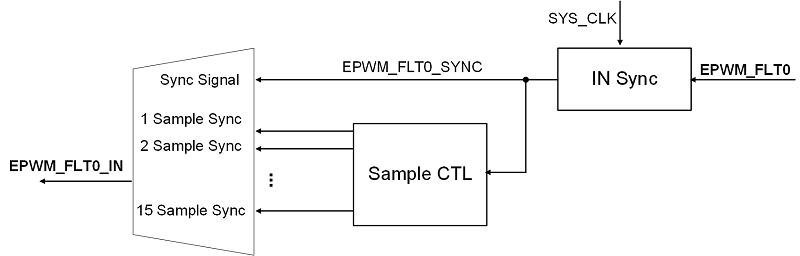

输入信号过滤

EPWM 保护模块的输入信号 EPWM_FLT0/1/2/3/4/5_IN,是经过输入信号过滤模块过滤的信号。输入信号过滤模块,用于滤除噪声信号,每路的输入信号都配置有对应的输入滤波模块:

-

同步信号输出:通过 SYS_CLK 对输入信号 EPWM_FLT0 进行同步。

-

1/2/…/15 采样点的同步信号输出:同步信号经过 Sample CTL 模块,判定 1/2/…/15 个采样点为相同值的信号认为有效信号,否则认为噪声信号进行滤除。

-

Sample CTL 模块的输入信号是 IN Sync 模块的输出信号,即 SYS_SCLK 对 EPWM_FLT0 信号进行同步得出 EPWM_FLT0_SYNC 信号。

-

通过配置 Sample CTL 模块的寄存器,可以配置对 EPWM_FLT0_SYNC 信号的采样周期,采样周期为 1x/ 2x/ 4x/ 6x/ …/ 510x SYS_CLK。

-

通过寄存器可以配置 1/2/…/15 采样点的同步信号输出,即以 1/2/…/15 个采样点的时间长度作为一个处理周期。若这个周期的采样点均为相同值则认为是有效值,EPWM_FLT0_IN 的信号输出此有效值。

-

- 在 T0 时刻,对 EPWM_FLT0_SYNC 进行第一次信号采集,采集为 0 信号。

- 接下来采集的四次信号均为 0 信号,因此在第五个采样点的时候,EPWM_FLT0_IN 进行了翻转,输出 0 信号,完成一个处理周期。

- 在 T1 时刻,由于第一次采集信号为 0 信号,而第二次采集信号出现 1 信号,此次处理周期判定为无效值,EPWM_FLT0_IN 维持当前值。

触发信号输出功能

EPWM 支持通过寄存器选择计数器不同时刻的触发信号,即 EPWM_CNT_Z、EPWM_CNT_PRD、EPWM_CNT_UAV、EPWM_CNT_DAV、EPWM_CNT_UBV、EPWM_CNT_DBV,通过外部 GPIO 输出。输出的触发信号,进行 8x SYS_CLK 的脉冲延长。

脉冲输出功能

脉冲输出功能用于产生固定脉冲数量,并且脉冲的频率和占空比均可以调整。利用 EPWM 的 A、B 通道输出,可以产生典型的方向脉冲、正交脉冲和 CW/CCW 脉冲信号。

脉冲输出

脉冲输出的功能,通过影子更新信号 PUL_CNT_ZRO,配合以下寄存器的影子更新实现:

-

PWM_CNT_PRDV:PWM 计数器的周期值,用于控制产生脉冲的周期。

-

PWM_CNT_AV:PWM 计数器比较 A 值。

-

PWM_CNT_BV:PWM 计数器比较 B 值。

-

PWMA_ACT:PWMA 动作寄存器。

-

PWMB_ACT:PWMB 动作寄存器。

-

PWMA_ACT_SW_CT:软件持续控制 PWMA 动作。

-

PWMB_ACT_SW_CT:软件持续控制 PWMB 动作。

-

PUL_OUT_NUM:输出脉冲设置,用于控制产生脉冲的数量。

影子更新信号 PUL_CNT_ZRO,可以通过寄存器的使能作为中断信号。以下三种方式可以产生 PUL_CNT_ZRO:

-

软件写寄存器字段EPWM_PUL_OUT_EN = 0x1,使能脉冲输出功能。

-

脉冲计数器完成脉冲数 NUM 的计数。

-

软件写寄存器字段EPWM_PUL_SW_UPDT = 0x1,强制产生一次 ZRO 的信号。

脉冲计数器的计数,可以通过寄存器字段 EPWM_PUL_CNT_SRC 选择不同触发信号作为脉冲计数器的信号源。 而脉冲数寄存器的配置,可以控制脉冲计数器需要的计数次数,计数次数为 (PUL_OUT_NUM + 1),在完成脉冲计数后,会产生一次 PUL_CNT_ZRO 信号,用于硬件自动更新影子寄存器。

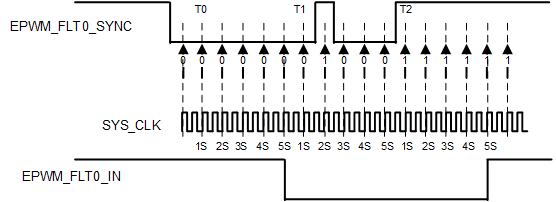

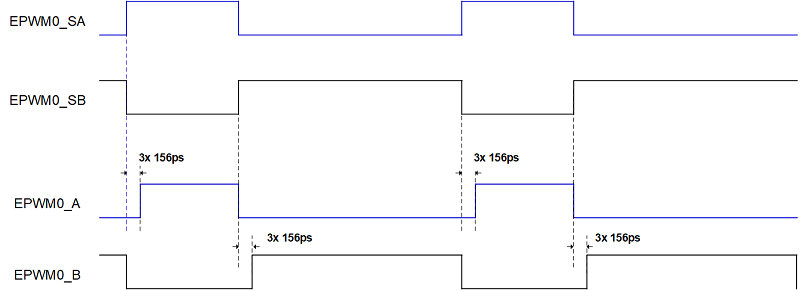

HRPWM 功能

HRPWM 功能仅有 EPWM0/1/2/…/5 支持,其它的 EPWM 模块不支持 HRPWM 功能。

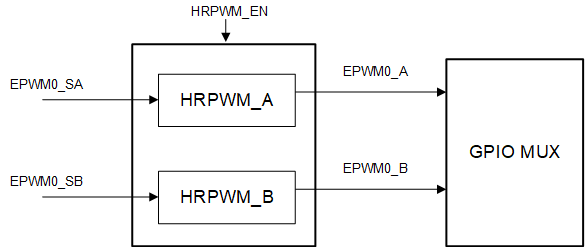

HRPWM 为 EPWM 模块输出的最后一级功能模块,HRPWM 能够对 A/B 通道输出信号的上升沿、下降沿或整体进行高精度边沿延迟,延迟的精度范围是 1x 156ps ~ 32x 156ps ,进而达到 EPWM 输出占空比或相位高精度的调节。PWMA 和 PWMB 均有独立的控制通道。

HRPWM 功能示例中,现 EPWM0_SA 和 EPWM0_SB 为互补信号,EPWM0 通过寄存器字段 HRPWM_EN = 0x1 使能 HRPWM 功能,寄存器字段 HRPWM_CHA_MODE = 0x0,选择上升沿延迟,寄存器字段 HRPWM_CHB_MODE = 0x0,选择上升沿延迟, 延迟时间 HRPWM_VAL_SET = 0x2,即 3x 156ps 的延迟。

EPWM0/1/…/5 的输出,需要打开 HRPWM 功能才可以输出信号,若不需要对 EPWM 进行高精度的边沿调整,只需要对寄存器字段 HRPWM_CHA_MODE 和 HRPWM_CHB_MODE 设置为 0x3,bypass HRPWM 功能即可。

Debug Hold 功能

调试进入断点模式,触发 EPWM 保护模式,进行 EPWM 的不可恢复输出保护,输出的电平由 EPWM 故障保护的寄存器决定。