功能描述

功能实现

由 DE 模块输入的 DI[23:0]、DE/HS/VS/CK 信号进到 2C1 处理输出信号选择 DATA_0[34:0] 以及 DATA_1[34:0],这里同时控制差分输出 Single Link 和 Dual Link。DI[23:0]、DE/HS/VS/CK 信号中的差分 CK 信号由寄存器配置,使用默认值即可。DATA_0[34:0] 以及 DATA_1[34:0] 分别进入 SER 转换成差分信号,如图 lvds_format。

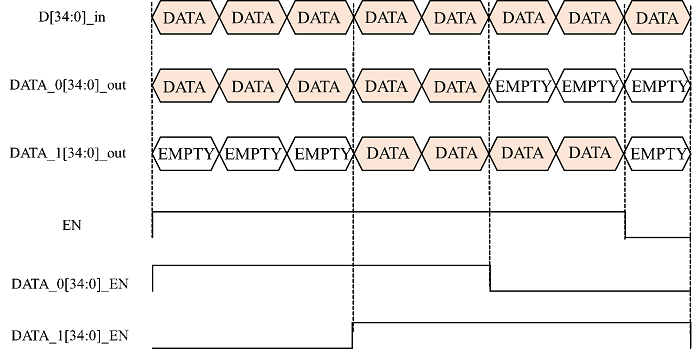

Single Link LVDS 输出控制方式:由 DE 模块输入的 24 位 RGB 信号、DE/HS/VS 以及寄存器配置的 7 位 CK 信号进行输出转换,当 EN 为低时,不做任何输出转换。

当 EN 为高时,若 DATA_0[34:0]_EN 为高,此时 DATA_0 进行输出转换:

-

若 DATA_1[34:0]_EN 为高,此时 DATA_1 进行输出转换;

-

若 DATA_0[34:0]_EN 以及 DATA_1[34:0]_EN 同时为高,则进行相同输出转换,此应用于双屏驱动。

图 10.36

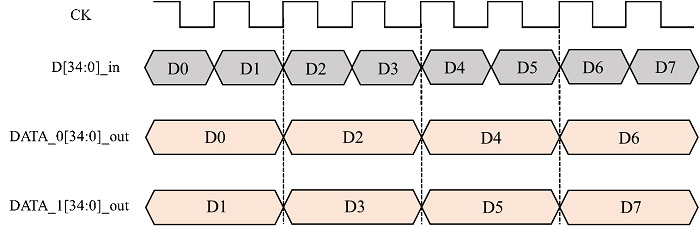

Dual lLink LVDS 输出控制模式: CK 第一个 cycle,D0 给到 DATA_0[34:0]。CK 第二个 cycle,D1 给到 DATA_1[34:0]。以此类推进行输出转换得到 lLink 输出。

-

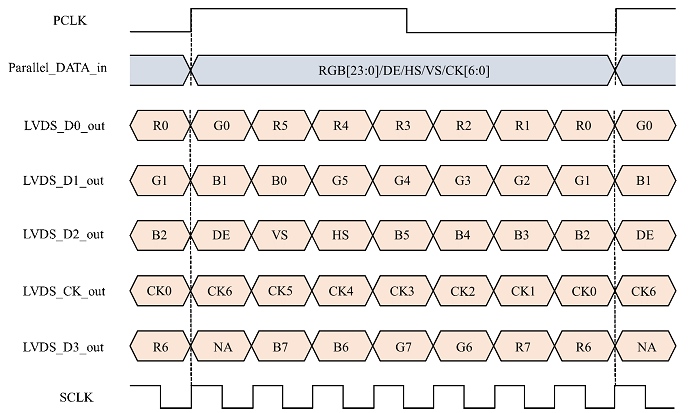

SCLK 的第一个 cycle,并行信号的 G0/B1/DE/CK6/NA 分别给到 LVDS_D0/ LVDS_D1/ LVDS_D2/ LVDS_CK/ LVDS_D3 的第一位。

-

SCLK 的第二个 cycle ,并行信号的 R5/B0/VS/CK5/NA 给到 LVDS_D0/ LVDS_D1/ LVDS_D2/ LVDS_CK/ LVDS_D3 第二位。

-

以此类推进行七个 SCLK cycle 数据转换,等到下一个 PCLK cycle 到达,并行信号同时更新,LVDS 信号按照同样的方式转换。

VESA-24 模式时序 (也称 NS 模式)

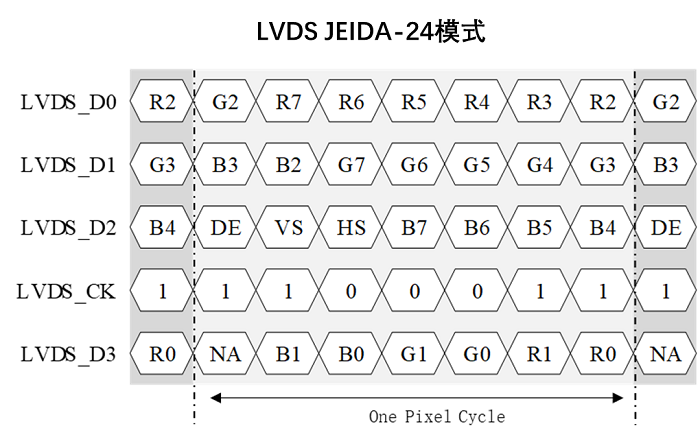

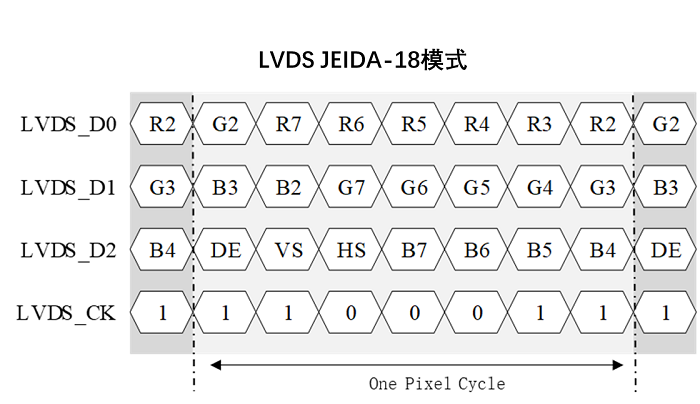

JEIDA 模式时序

其中 R7-R2 对应 6bit 屏信号的 R5-R0。G7-G2 对应 6bit 屏信号的 G5-G0。B7-B2 对应 6bit 屏信号的 B5-B0。