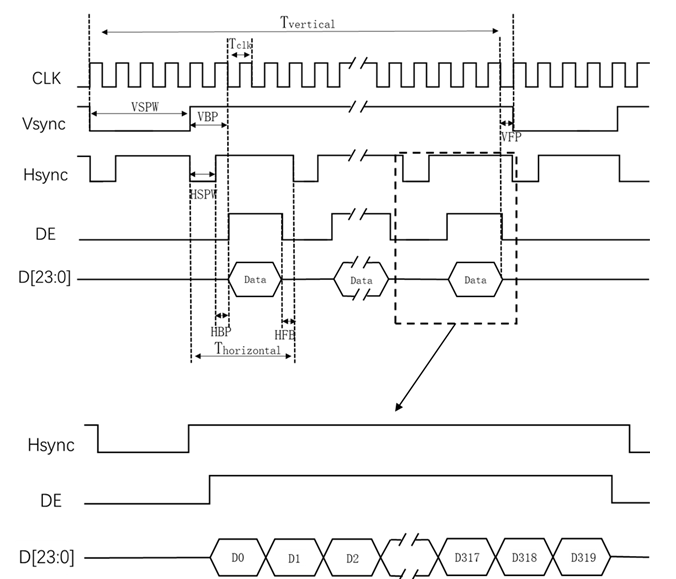

PRGB 接口时序

Vsync 为帧同步信号,表示帧开始。Hsync 为行同步信号,表示行开始。DE 为数据有效使能,表示数据有效,每 1 个 CLK 周期,采样一个像素数据 D[23:0],以此完成一帧图像的输出显示。

Defined |

Function |

|---|---|

CLK |

像素时钟 |

Vsync |

帧同步信号 |

Hsync |

行同步信号 |

DE |

数据有效使能 |

D[23:0] |

像素数据信号 |

Tclk |

时钟周期 |

Tvertical |

列扫描周期 |

Thorizontal |

行扫描周期 |

VBP |

列扫描后肩 |

VFP |

列扫描前肩 |

VSPW |

列同步信号脉宽 |

HBP |

行扫描后肩 |

HFP |

行扫描前肩 |

HSPW |

行同步信号脉宽 |

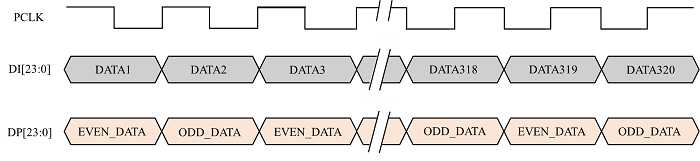

数据块选择以及并转串功能

由 DE 模块输入的 DI[23:0] 信号进到 FMT 进行格式转换,输出并行 RGB 数据 DP[23:0] 信号,如下图所示。

其中 DP[23:0] 每 8 位数据可任意互换输出 R/G/B 信号或者输出用户设置的 data 数据,用于功能调试以及方便 layout 走线, DP[23:0] 再进入到 SER0 转换成串行 RGB 数据 DS[7:0] 信号,如 lcd_srgb 所示。

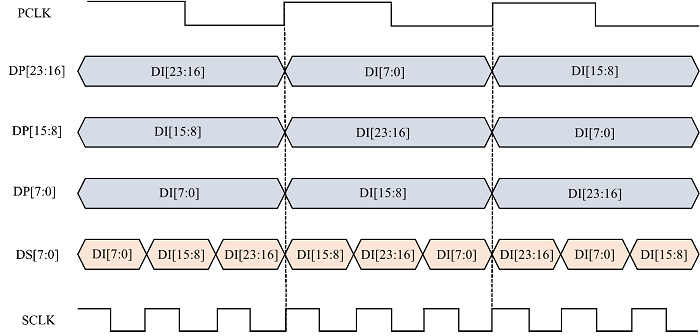

并行信号转串行信号控制方式:

- DE 模块输入的完整图片 RGB 信号 DI[23:0] 分为以下三组,进入 FMT 转换 DP 输出,用户可自由配置。

- DI[23:16]

- DI[15:8]

- DI[7:0]

例如 DP[7:0],可通过配置输出 DI[23:16]、 DI[15:8] 或者 DI[7:0] 的数据。

- 之后三组 DP 信号进入 SER0 进行并行转串行。一个 PCLK 内:

- DP[7:0] 的数据在第一个 SCLK cycle 给到 DS[7:0]。

- DP[15:8] 的数据在第二个 SCLK cycle 给到 DS[7:0]

- DP[23:16] 的数据在第三个 SCLK cycle 给到 DS[7:0],以此循环。

注:无论三组 DP 信号里存着任何的 DI 数据,在并行信号转串行信号过程中均为 DP[7:0]/ DP[15:8]/ DP[23:16] 依次给到 DS[7:0]。 - 配置下列相关寄存器:

R/ G/ B 组内数据输出顺序切换功能

组内数据顺序切换:

以 8 bits 为单位进行切换,D23-D16/ D15-D8/ D7-D0 三组。

示例 1:D7-D0 组默认输出 D7-D6-D5-D4-D3-D2-D1-D0,可切换成顺序 D0-D1-D2-D3-D4-D5-D6-D7。

关于详细说明,可查看相关配置寄存器DATA_QUT_SEL。