功能描述

PLL

模拟电路 PLL 用于产生时钟供给整个芯片。

名称 |

用途 |

典型频率 |

展频 |

|---|---|---|---|

PLL_INT0 |

CPU |

480 MHz |

不支持 |

PLL_INT1 |

AXI/ AHB/ APB/ CE/ DE/ GE/ VE/ DVP/ PWMCS/ TA_IF/ EDAT_IF/ BIS_IF/ SDFM/ UART/ PWM/ I2S/ AUDIO |

1.2 GHz |

不支持 |

PLL_FRA0 |

XSPI/ SPI/ SDMC |

792 MHz |

展频 |

PLL_FRA2 |

LCD/ LVDS/ MIPI_DSI |

- |

展频 |

PLL 内部结构如下图所示, PLL 频率计算公式为:PLL_OUT = 24 MHz × (N + 1 + F÷0x1FFFF)/(P+1)/(M+1)。其中,F 为 FRA_IN 小数分频系数,当不使用小数分频时,F=0,频率计算公式简化为:PLL_OUT = 24 MHz × (N + 1)/(P + 1) ÷(M+1)

PLL 配置流程

- PLL 输出配置旁路为 24 MHz, PLL_FRAn_GEN.PLL_OUT_MUX = 0,选择为 24M 时钟

- PLL 电路关闭, PLL_FRAn_GEN.PLL_EN = 0

- PLL 频率系数配置, PLL_FRAn_GEN.FACTOR_P,PLL_FRAn_GEN.FACTOR_N,PLL_FRAn_GEN.FACTOR_M,PLL_FRAn_GEN.FACTOR_M_EN

- PLL 展频/小数分频配置, PLL_FRAn_CFG PLL_FRAn_SDM

- PLL 电路打开, PLL_FRAn_GEN.PLL_EN = 1,延迟 200 us

- PLL 输出使能, PLL_FRAn_GEN.PLL_OUT_EN = 1

- PLL 输出配置切换为高频时钟, PLL_FRAn_GEN.PLL_OUT_MUX = 1

展频配置

- 展频幅度:寄存器为 PLL_FRAn_SDM.SDM_BOT,对应幅度为 24 MHz / (P + 1) × (0x1FFFF − SDM_BOT) ÷ 0x1FFFF

- 展频频率:寄存器为 PLL_FRAn_SDM.SDM_FREQ,建议设置为 3 (33 KHz)

- 展频模式:寄存器为 PLL_FRAn_SDM.SDM_MODE,建议设置为 2 (三角波)

- 根据展频幅度需求,求得 SDM_BOT = 0x1FFFF − SDM_AMP*0x1FFFF × (P+1) / 24 MHz

- 根据展频频率需求,求得 STEP_NUM = 24 MHz ÷ (P + 1) ÷ (SDM_FREQ ÷ 2) = 24000000 ÷ (P+1) ÷ (33000/2)

- 根据展频幅度和展频步数,求得 SDM_STEP = (0x1FFFF− SDM_BOT) ÷ STEP_NUM

- PLL_FRAn_SDM.SDM_STEP 设置值需要和展频幅度和展频频率匹配,以产生正常的展频波形

- 当 P=0 时,最大展频幅度为 24 MHz,如果 N=32,则 PLL 频率为 792 MHz,展频深度为 24/792 ≈ 3.0%

- 当 P=1 时,最大展频幅度为 12 MHz,如果 N=65,则 PLL 频率为 792 MHz,展频深度为 12/792 ≈ 1.5%

CLKOUT

时钟输出用于输出时钟给芯片外设使用, 总共四路 CLKOUT,可选来源为 PLL_INT1/PLL_FRA2,可配置 1~256 除频, CLKOUT 通路如下图所示。

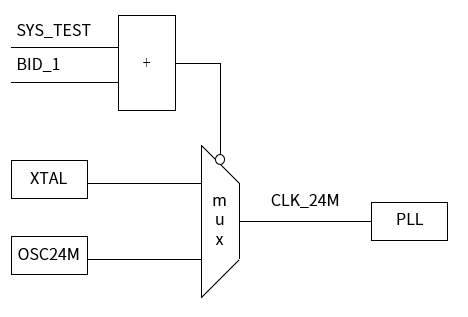

OSC24M 和 XTAL

- 内部 OSC24M

- 外部 XTAL。

-

当引脚 SYS_TEST 配置的值为 1 时,无论 BID_1 为何值,只能选择外部 XTAL 作为芯片时钟源输入。

-

当引脚 SYS_TEST 配置的值为 0 时,根据 BID_1 的值选择芯片的输入时钟源:

- 若 BID_1 值为 1,则选择外部 XTAL 时钟源。

- 若 BID_1 值为 0,则选择内部 OSC24M 时钟源。

模块时钟

模块名称 |

总线时钟 |

模块时钟源 |

模块时钟极限频率 |

备注 |

|---|---|---|---|---|

E907 CORE |

- |

PLL_INT0 |

480 MHz |

- |

E907 PLIC |

- |

PLL_INT0÷2 |

240 MHz |

- |

E907 CLINT |

- |

PLL_INT0÷2 |

240 MHz |

- |

E907 DM |

- |

CLK_24M |

24 MHz |

- |

AXI |

AXI |

- |

200 MHz |

- |

AHB |

AHB |

- |

200 MHz |

- |

APB0 |

APB0 |

- |

100 MHz |

- |

APB1 |

APB1 |

- |

24 MHz |

- |

BROM |

AXI |

- |

- |

- |

SRAM |

AXI |

- |

- |

- |

AHB Matrix |

AHB |

- |

- |

- |

DMA |

AHB |

- |

- |

- |

CE |

AHB |

PLL_INT1 |

200 MHz |

- |

USB DEV |

AHB |

- |

- |

- |

USB PHY |

- |

CLK_24M |

- |

- |

EMAC |

AHB |

PLL_INT1 |

50 MHz |

- |

XSPI |

AHB |

PLL_FRA0 |

400 MHz |

- |

SPI0 |

AHB |

PLL_FRA0 |

100 MHz |

- |

SPI1 |

AHB |

PLL_FRA0 |

100 MHz |

- |

SPI2 |

AHB |

PLL_FRA0 |

100 MHz |

- |

SPI3 |

AHB |

PLL_FRA0 |

100 MHz |

- |

CORDIC |

AHB |

- |

- |

- |

HCL |

AHB |

- |

- |

- |

PBUS |

AHB |

- |

- |

- |

SYSCFG |

APB0 |

CLK_24M |

24 MHz |

- |

CMU |

APB0 |

- |

- |

- |

SPI_ENC |

APB0 |

HCLK |

- |

- |

PWMCS |

APB0 |

PLL_INT1 |

200 MHz |

- |

ADC |

APB0 |

PLL_INT1 |

100 MHz |

- |

AXICFG |

APB0 |

- |

- |

- |

MTOP |

APB0 |

- |

- |

- |

I2S |

APB0 |

PLL_INT1 |

26 MHz |

- |

AUDIO |

APB0 |

PLL_INT1 |

26 MHz |

- |

GPIO |

APB0 |

- |

- |

- |

UART0 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART1 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART2 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART3 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART4 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART5 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART6 |

APB0 |

PLL_INT1 |

60 MHz |

- |

UART7 |

APB0 |

PLL_INT1 |

60 MHz |

- |

TA_IF |

APB0 |

PLL_INT1 |

240 MHz |

- |

EDAT-IF |

APB0 |

PLL_INT1 |

240 MHz |

- |

BIS_IF |

APB0 |

PLL_INT1 |

240 MHz |

- |

SDFM |

APB0 |

PLL_INT1 |

240 MHz |

- |

LCD |

APB0 |

PLL_FRA2 |

400 MHz |

DISP_PIXCLK:200MHz |

LVDS |

APB0 |

PLL_FRA2 |

1000 MHz |

DISP_PIXCLK: 200 MHz |

DSI |

APB0 |

PLL_FRA2 |

1200 MHz |

DISP_PIXCLK: 200 MHz |

DVP |

APB0 |

PLL_INT1 |

200 MHz |

- |

DE |

APB0 |

PLL_INT1 |

200 MHz |

DISP_PIXCLK: 200 MHz |

GE |

APB0 |

PLL_INT1 |

200 MHz |

- |

VE |

APB0 |

PLL_INT1 |

200 MHz |

- |

WDOG |

APB1 |

CLK_32K |

32 KHz |

- |

WRI |

APB1 |

CLK_24M |

24 MHz |

- |

SID |

APB1 |

CLK_24M |

24 MHz |

- |

RTC |

APB1 |

XTAL_32K |

1 MHz |

- |

GTC |

APB1 |

- |

- |

- |

I2C0 |

APB1 |

- |

- |

- |

I2C1 |

APB1 |

- |

- |

- |

I2C2 |

APB1 |

- |

- |

- |

I2C3 |

APB1 |

- |

- |

- |

CAN0 |

APB1 |

- |

- |

- |

CAN1 |

APB1 |

- |

- |

- |

PWM |

APB1 |

PLL_INT1 |

100 MHz |

- |

ADCIM |

APB1 |

PLL_INT1 |

100 MHz |

- |

THS |

APB1 |

- |

- |

- |

CPM |

APB1 |

- |

- |

- |

UART 在 PLL_INT1=1.2GHz 下波特率精度

设定波特率 |

实际波特率 |

波特率偏差 |

CMU 除频 |

Over sampling |

Clock source |

UART 除频 |

|---|---|---|---|---|---|---|

300 |

300 |

0 |

25 |

16 |

48000000 |

10000 |

600 |

600 |

0 |

25 |

16 |

48000000 |

5000 |

1200 |

1200 |

0 |

25 |

16 |

48000000 |

2500 |

2400 |

2400 |

0 |

25 |

16 |

48000000 |

1250 |

4800 |

4800 |

0 |

25 |

16 |

48000000 |

625 |

9600 |

9615 |

0.16 |

25 |

16 |

48000000 |

312 |

14400 |

14423 |

0.16 |

25 |

16 |

48000000 |

208 |

19200 |

19230 |

0.16 |

25 |

16 |

48000000 |

156 |

38400 |

38461 |

0.16 |

25 |

16 |

48000000 |

78 |

57600 |

57692 |

0.16 |

25 |

16 |

48000000 |

52 |

115200 |

115384 |

0.16 |

25 |

16 |

48000000 |

26 |

230400 |

230769 |

0.16 |

25 |

16 |

48000000 |

13 |

380400 |

378787 |

-0.42 |

22 |

16 |

54545454 |

9 |

460800 |

462963 |

0.47 |

27 |

16 |

44444444 |

6 |

921600 |

925925 |

0.47 |

27 |

16 |

44444444 |

3 |

1000000 |

1000000 |

0 |

25 |

16 |

48000000 |

3 |

1152000 |

1136363 |

1.36 |

22 |

16 |

54545454 |

3 |

1500000 |

1500000 |

0 |

25 |

16 |

48000000 |

2 |

2500000 |

2500000 |

0 |

30 |

16 |

40000000 |

1 |

3000000 |

3000000 |

0 |

25 |

16 |

48000000 |

1 |

模块开关控制和时序

模块一般有三个控制位:

- MOD_RSTN(模块复位控制):同时复位模块和模块总线。

- MOD_BUS_EN(模块总线时钟开关):控制模块的所有总线时钟,包括 AX、AHB 和 APB,如果模块使用到多个总线,由于只有一个控制位,该控制位同时控制多个总线时钟。

- MOD_CLK_EN(模块时钟开关): 控制除了总线时钟以外的模块时钟,如果模块用到多个时钟,由于只有一个控制位,该控制位同时控制多个模块时钟。

| 模块 | 打开时序 | 关闭时序 |

|---|---|---|

| USB_DEV |

|

|

| 标准模块 |

|

|

| 标准模块 |

注:

模块无对应控制位即不进行设置 |

注:

模块无对应控制位即不进行设置 |