数据缓冲器

寄存器 |

偏移地址 |

标准格式内容 |

扩展格式内容 |

|---|---|---|---|

CAN_BUF0 |

0x40 |

TX/RX 帧信息 |

TX/RX 帧信息 |

CAN_BUF1 |

0x44 |

TX/RX 标识符 1 |

TX/RX 标识符 1 |

CAN_BUF2 |

0x48 |

TX/RX 标识符 2 |

TX/RX 标识符 2 |

CAN_BUF3 |

0x4C |

TX/RX 数据 1 |

TX/RX 标识符 3 |

CAN_BUF4 |

0x50 |

TX/RX 数据 2 |

TX/RX 标识符 4 |

CAN_BUF5 |

0x54 |

TX/RX 数据 3 |

TX/RX 数据 1 |

CAN_BUF6 |

0x58 |

TX/RX 数据 4 |

TX/RX 数据 2 |

CAN_BUF7 |

0x5C |

TX/RX 数据 5 |

TX/RX 数据 3 |

CAN_BUF8 |

0x60 |

TX/RX 数据 6 |

TX/RX 数据 4 |

CAN_BUF9 |

0x64 |

TX/RX 数据 7 |

TX/RX 数据 5 |

CAN_BUF10 |

0x68 |

TX/RX 数据 8 |

TX/RX 数据 6 |

CAN_BUF11 |

0x6C |

保留 |

TX/RX 数据 7 |

CAN_BUF12 |

0x70 |

保留 |

TX/RX 数据 8 |

- 发送缓冲寄存器:CPU 对数据缓冲寄存器组的写操作访问,配置待发送报文,指定报文的帧类型、帧格式、帧标识符和数据。CPU 通过控制寄存器 CAN_MCR

配置发送报文模式:

- 正常报文发送:TX_REQ 置 1。

- 自发自收:SELF_REQ 置 1。

- 单次发送:TX_REQ 和 ABORT_REQ 同时置 1。

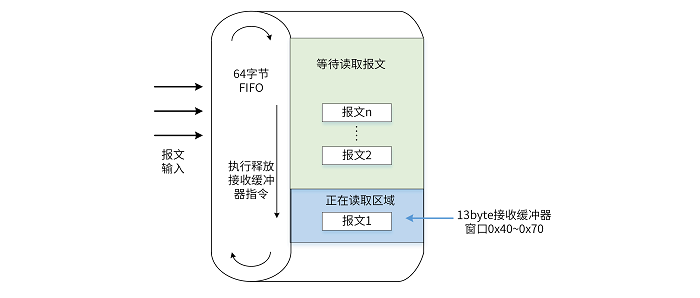

- 接收缓冲寄存器:CPU 对数据缓冲寄存器组的读取操作访问,接收缓冲寄存器映射到缓冲 FIFO

中的第一条报文,获取第一条报文的帧类型、帧格式、帧标识符和数据。

读取完接收缓冲寄存器中的报文后,CPU 通过控制寄存器 CAN_MCR 中的 RXB_REL 置 1 来释放接收缓冲寄存器。

若接收 FIFO 中仍有待处理的报文,按照接收报文的先后次序,将最早接收到的报文映射到接收缓冲寄存器中。

- 缓冲 FIFO: 是一个 64 字节大小的内部缓冲器,以先进先出原则存储接收到的报文。

- 接收缓冲寄存器为 FIFO 中可访问窗口,偏移地址 0x40~0x70,将被映射到 FIFO 中的第一条报文。

一条报文可在 FIFO 中占 3 ~ 13 字节空间,其中字节序与接收缓冲寄存器相同。

- 当控制器接收到一条报文时,接收数据计数器 RXC 增加 1,最大值为 64。

如果 FIFO 中有足够空间,报文内容将被写入到 FIFO 中。

- CPU 读取接收缓冲寄存器中的报文后,通过将 RXB_REL 置 1,释放 FIFO 中第一条报文所占的空间,RXC 将减小 1。

- 接收缓冲寄存器接着映射 FIFO 中的下一条报文。

- 接收缓冲寄存器为 FIFO 中可访问窗口,偏移地址 0x40~0x70,将被映射到 FIFO 中的第一条报文。

- FIFO 数据溢出:任何情况下,FIFO 中可以存储的报文数量取决于各条报文的长度。当 FIFO

中没有足够空间完整地存储新报文时,控制器会产生数据溢出,通过状态位或数据溢出中断反馈给 CPU。

FIFO 在内部将溢出报文标记为无效,后续接收到的溢出报文仍然将增加 RXC 到最大值 64。为了读取接收 FIFO 中的所有有效报文并清除所有溢出报文,应重复调用 RXB_REL,直到 RXC 为 0。