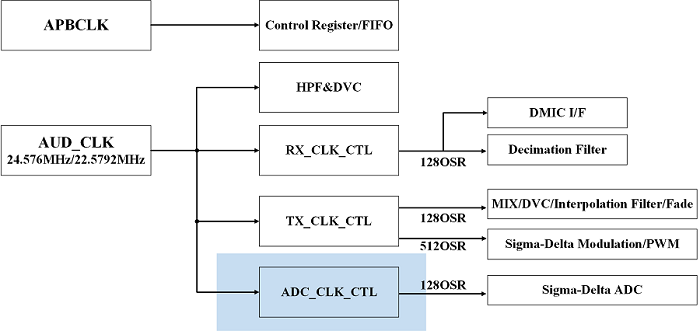

Audio Codec 时钟

如图所示:

- APBCLK:用于控制寄存器以及 FIFO 。

- AUD_CLK:24.576 MHz / 22.5792 MHz 由 CMU 分频所得,同时提供给 TX(播放)和 RX(录音)部分。RX 部分通过寄存器 FS_DMIC_IN 配置了 RX 的采样频率:

-

相应的过采样率 128 倍的时钟提供给 DMIC I/F 模块以及 Decimation Filter。

-

RX 部分的 HPF 以及 DVC 的时钟则由 AUD_CLK 直接提供。

TX 部分通过寄存器 FS_OUT 配置了 TX 的采样频率:

-

相应的过采样率 128 倍的时钟提供给 MIX、DVC、Interpolation Filter、Fade 模块。

-

过采样率 512 倍的时钟则提供给 Sigma-Delta Modulation、PWM 模块。

-

- Sigma-Delta ADC 利用 AUD_CLK 时钟信号产生 ADC 所需要的时钟信号。