脉冲输出模式

- PWM_PRD

- PWM_CMP

- 输出脉冲数量的寄存器 PUL_CNT

- PUL_CNT 寄存器进行了写的操作。

- REG_UPDT 有效信号的到来。

脉冲输出支持以下两种更新模式,通过配置 PWM_UPDATE_MODE 进行选择:

- 硬件更新:

在 FIFO 模式下,FIFO 不为空时自动加载数据,非 FIFO 模式 IDLE 状态下写 PUL_CNT 会触发寄存器的影子更新。

- 软件更新

在 IDLE 下需要软件触发 resume 产生 REG_UPDT 信号,触发寄存器的影子更新。

脉冲输出模式支持三种方式实现脉冲输出的功能,分别是自由方式 (未采用中断和 DMA)、持续方式 (采用中断)、FIFO(采用中断或 DMA)方式。

自由方式

自由方式输出脉冲,每设置一次发送脉冲数量的数值,PWM 输出则发送相应数量的脉冲后则处于一直 IDLE 的状态 (IDLE 状态可以设置为输出高电平或低电平)。以下为自由配置方式的脉冲输出例子:

如上图所示,为使用软件更新自由方式的脉冲输出,对应的说明如下:

- 在脉冲输出的模式下,使能 PWM 的计数器,即 PWM_CNT_EN 从 0x0 跳变 0x1,此时产生一次的 REG_UPDT,即进行一次的寄存器更新。如上图的 T0 时刻。

- 如上图,经过 T0 时刻的 REG_UPDT,PWM_PRD、PWM_CMP 和 PUL_CNT 加载影子寄存器的数值,即生效寄存器的情况为 PWM_PRD_ACT = PRD0、PWM_CMP_ACT = CMP0 和 PUL_CNT_ACT = 2。此时 PWM 的计数器开始计数,从零开始计数至 PRD0,在计数至 PRD0 触发一次 TRI_PUL_CNT,进而触发 PUL_CNT_ACT 自减一,此时 PWM 输出一个脉冲信号。如此重复,PWM 计数器再完成一次从零递增至 PRD0,PWM 再输出一个脉冲信号,并且此时 ACT 自减一,PUL_CNT_ACT = 0。

- 在 PUL_CNT_ACT 跳变至零的时刻,产生一次 REG_UPDT 有效信号。如上图的例子,T1 时刻产生了一次有效的 REG_UPDT 信号,但是由于没有发生对 PUL_CNT 寄存器的写操作,此时并不会进行一次影子更新。

- 在 PUL_CNT_ACT = 0 的状态下,进入 IDLE 状态,PWM 的计数器停止计数,上述例子中,PWM 的输出信号强制设置为低电平状态 (此状态可以通过寄存器配置为高/低电平)。

- 如上图示例,在 T3 时刻软件通过对寄存器字段 PUL_RESUME 写入 0x1,产生了一次的 REG_UPDT 有效信号,由于在 T2 时刻已对 PUL_CNT 寄存器进行写操作,所以此次的 REG_UPDT 会进行影子寄存器的更新。另外这里会将计数器重置为零开始计数。

- 从 T4 时刻到 T6 时刻均为类似的过程。

- 最后上图的 T7 时刻,将 PWM_CNT_EN 拉低为 0x0,PWM 计数器停止计数回到零,PWM_PRD、PWM_CMP 和 PUL_CNT 的影子寄存器均自动清零,PWM 的输出为 IDLE 状态。

如上图所示,为使用硬件更新自由方式的脉冲输出,对应的说明如下:

- 硬件更新和软件更新类似,在 T0 时刻使能 PWM,脉冲信号开始输出。

- T2 时刻,在 IDLE 状态对 PUL_CNT 寄存器进行写操作,会触发影子寄存器的更新,脉冲信号开始输出。T5 时刻类似。

- 最后 T7 时刻,PWM_CNT_EN 拉低为 0x0,PWM 计数器停止计数回零,PWM 的输出为 IDLE 状态。

持续方式

中断方式输出脉冲,即通过中断,每次中断函数设置下次发送脉冲数量的数值,PWM 输出则一直按照设置的数值持续发送脉冲。以下为持续方式的脉冲输出例子:

如上图所示,为使用软件更新持续方式的脉冲输出,其中 REG_UPDT 信号在更新寄存器后同时产生中断信号通知 CPU 进入中断函数,对应的说明如下:

- 在 T0 时刻之前,PWM_CNT_EN = 0x0,写入一次 PRD、PWM_CMP 和 CNT 的影子寄存器数值,PWM_PRD = PRD0、PWM_CMP = CMP0 和 PUL_CNT = 2。

- 在 T0 时刻使能 PWM 的计数器进行计数,PWM_CNT_EN = 0x1,这时产生一次 REG_UPDT,进行一次的寄存器更新,更新 T0 时刻之前写入的数值。更新的同时也产生一次中断信号进入中断函数,中断函数需要写入下一次的影子寄存器的数值,这里的设置是 PWM_PRD = PRD1、PWM_CMP = CMP1 和 PUL_CNT = 4。

- 在 T1 时刻,PUL_CNT_ACT 会从 0x1 递减至 0x0,并且产生一次寄存器更新信号 REG_UPDT,加载了新的影子寄存器值。

- 在 T 1 时刻更新寄存器的同时也会进入中断函数,软件会再写入下一次的影子寄存器值,PWM_PRD = PRD1、PWM_CMP = CMP1 和 PUL_CNT = 0。

- 在 T2 时刻,更新了脉冲输出数为零的情况,此时 PWM 输出为 IDLE 状态。需等待 PUL_RESUME 信号的到来才可以继续进行脉冲输出的功能。

- 在 T3 时刻,软件更新出现软件写 PUL_RESUME = 0x1,此时会产生一次的 REG_UPDT 有效信号。进行影子寄存器的更新并且计数器复位为零,这样脉冲输出的功能则按照之前的同样方式持续进行。

- 最后在 T4 时刻,PWM_CNT_EN = 0x0,计数器停止计数,输出为 IDLE 状态。

如上图所示,为使用硬件更新持续方式的脉冲输出,其中 REG_UPDT 信号在更新寄存器后同时产生中断信号通知 CPU 进入中断函数,对应的说明如下:

- T2 时刻前,硬件更新与软件更新一致,寄存器更新的同时也产生一次中断信号进入中断函数,中断函数需要写入下一次的影子寄存器的数值,脉冲信号持续输出。

- T2 时刻,更新的脉冲输出数为零的情况,PWM 输出为 IDLE 状态。T3 时刻写入 PUL_CNT,会进行影子寄存器的更新并且计数器复位为零,这样脉冲输出的功能则按照之前的同样方式持续进行。

- 最后在 T4 时刻,PWM_CNT_EN = 0x0,计数器停止计数,输出为 IDLE 状态。

FIFO 方式

FIFO 方式输出脉冲,是利用内置的 FIFO 对影子寄存器更新的方式,实现持续发送脉冲。这样相对上面提到的持续方式,可以大大提高脉冲输出的效率,避免频繁进入中断函数。

针对 FIFO 方式的脉冲输出功能,内置了 24 * 32-bit 的 FIFO,用于存放 PUL_CNT、PWM_PRD、PWM_CMP。在触发信号 REG_UPDT 的作用下,FIFO 可以依次往 XPMW_PRD、PWM_CMP、PUL_CNT 进行写入新的影子寄存器值,因此 FIFO 写入也需按此顺序依次写入。

另外此 FIFO 支持 DMA 或中断的方式写入,通过设置 FIFO 的阈值,使能 DMA 请求或 FIFO 中断信号,即可进行数据的写入。

以下为 FIFO 方式的脉冲输出例子:

如上图所示,为软件更新 FIFO 方式的脉冲输出,其中 REG_UPDT 信号在更新寄存器后同时产生,触发 FIFO 进行更新影子寄存器的数值,对应的说明如下:

- 在 T0 时刻之前,即 PWM_CNT_EN = 0x0,FIFO 需提前备好数据,可以通过中断或 DMA 进行写入。

- 在 T0 时刻使能 PWM 的计数器进行计数,PWM_CNT_EN = 0x1,这时产生一次的 REG_UPDT,进行一次的寄存器更新,更新 T0 时刻之前写入的数值。更新的同时触发 FIFO 发送数据写入下一次的 PWM_PRD、PWM_CMP 和 PUL_CNT,这里的设置是 PWM_PRD = PRD1、PWM_CMP = CMP1 和 PUL_CNT = 4。

- 在 T1 时刻,PUL_CNT_ACT 从 0x1 递减至 0x0,并且产生一次寄存器更新信号 UPDT,加载了新的影子寄存器值。

- T1 时刻更新寄存器之后 ,FIFO 随后也写入新的影子寄存器的数值,PWM_PRD = PRD1、PWM_CMP = CMP1 和 PUL_CNT = 0。

- 在 T2 时刻,更新了脉冲输出数为零的情况,此时 PWM 输出为 IDLE 状态。需等待 PUL_RESUME 信号的到来才可以继续进行脉冲输出的功能。

- 在 T3 时刻,出现软件写 PUL_RESUME = 0x1,此时会重置计数器为零,并且产生一次 UPDT 有效信号,这样脉冲输出的功能则按照之前的同样方式持续进行。

- 最后在 T4 时刻,PWM_CNT_EN = 0x0,计数器停止计数,输出为 IDLE 状态。

如上图所示,为硬件更新 FIFO 方式的脉冲输出,其中 REG_UPDT 信号在更新寄存器后同时产生,触发 FIFO 进行更新影子寄存器的数值,对应的说明如下:

T2 时刻前,硬件更新和软件更新一致。当 T2 时刻,PWM 输出为 IDLE 状态且此时 FIFO 不为空,硬件更新自动加载配置,更新影子寄存器继续输出脉冲信号。

软件触发 RESUME 功能

软件触发,可以通过对寄存器字段 PUL_RESUME 写 0x1,硬件产生一次 REG_UPDT 触发信号,该触发信号能够强制进行一次对 PUL_CNT、PWM_PRD、PWM_CPM 寄存器的影子更新,并且强制 CNT 复位至零。

脉冲数量统计功能

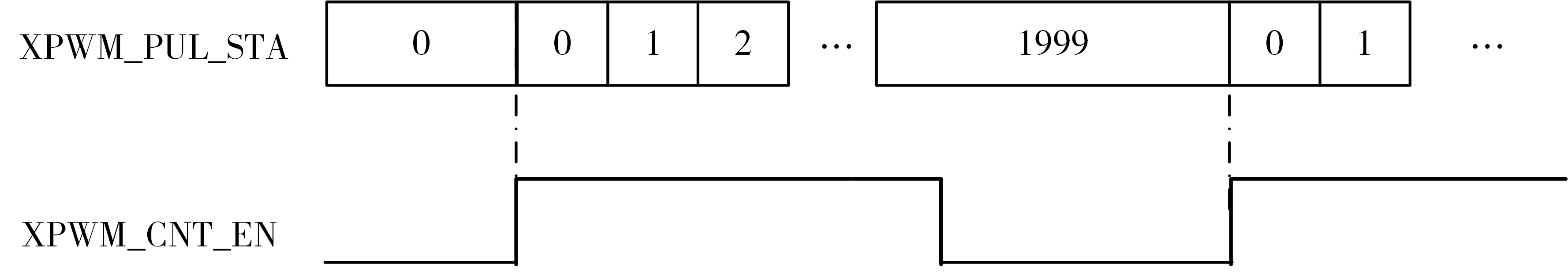

在脉冲输出模式下,支持对发送脉冲数量的统计,统计的数量保存在寄存器 PWM_PUL_STA 中。

如下图所示,在 PWM_CNT_EN = 0x1 的时刻 (即上升沿),PWM_PUL_STA 寄存器自动清零,从零开始统计发送的脉冲数量。在 PWM_CNT_EN 从 0x1 跳变为 0x0,此时 PWM_PUL_STA 寄存器保持当前的数据,只有在下一次的 PWM_CNT_EN 使能或对 PWM_PUL_STA_FLUSH 写 1,才会自清零开始下一次的脉冲数量统计。

脉冲数量限制功能

在脉冲输出模式下,通过设置寄存器字段 PUL_LIMIT_EN = 0x1 可以使能脉冲数量限制的功能。脉冲数量限制功能是当前已发送脉冲数量 PWM_PUL_STA 等于所设置的脉冲阈值 PUL_THR 时,会触发中断状态 PWM_PUL_LIMIT。

当 PWM 达到 PUL_THR 后,PWM 的计数器停止计数,脉冲也会停止输出。如需继续按照之前的配置情况重新启动 PWM,则对寄存器字段 PUL_THR_RS 写 0x1,触发 PWM 的计数器继续进行计数。需注意此时需要配置新的 PUL_THR,否则会一直存在已发送脉冲数量 PWM_PUL_STA 大于 THR 的情况。

强制脉冲输出功能

在脉冲输出模式下,对 PUL_CNT 写入 0xFFFF FFFF 后,脉冲输出进入强制输出模式,在此模式下,PWM 持续发送脉冲,发送脉冲的频率和占空比可以通过 PWM_PRD 和 PWM_CPM 寄存器动态调整。此时脉冲数量统计以及脉冲数量限制的功能仍然生效。

如需退出强制脉冲输出功能,则需通过对 PUL_CNT 写入非 0xFFFF FFFF 的脉冲数量值,然后在对寄存器 PUL_RESUME 写 0x1,触发一次软件更新信号,进行 CNT 的更新。

另外,在进入强制脉冲输出模式的时刻,支持触发中断信号 PWM_FRC_PUL。

中断信号

在脉冲输出的模式下,支持的中断信号包括如下:

- REG_UPDT,更新寄存器信号中断

- FIFO_AVAL,FIFO Available 信号中断,即 FIFO 的数据低于设定阈值时产生的中断信号

- FIFO_EMPTY,FIFO 空信号中断,即此时 FIFO 无数据

- FIFO_FULL,FIFO 满信号中断,即此时 FIFO 已满

- PWM_FRC_PUL,输出进入了强制输出脉冲模式

- PWM_PUL_LIMIT,脉冲数量达到限制值 PUL_THR