功能描述

设备

|

设备模块 |

DMA_ID |

位宽 (bit) |

Burst(最大) |

地址 |

|---|---|---|---|---|

| SRAM/ PSRAM/ XIP | 0 | 32 | 16 | 递增 |

|

DMA_ID_SPI0 |

10 |

8/32 |

16 |

保持 |

|

DMA_ID_SPI1 |

11 |

8/32 |

16 |

保持 |

|

DMA_ID_AUDIO |

14 |

32 |

1 |

保持 |

|

DMA_ID_UART0 |

16 |

8 |

1 |

保持 |

|

DMA_ID_UART1 |

17 |

8 |

1 |

保持 |

|

DMA_ID_UART2 |

18 |

8 |

1 |

保持 |

|

DMA_ID_UART3 |

19 |

8 |

1 |

保持 |

|

DMA_ID_XSPI |

24 |

8 |

16 |

保持 |

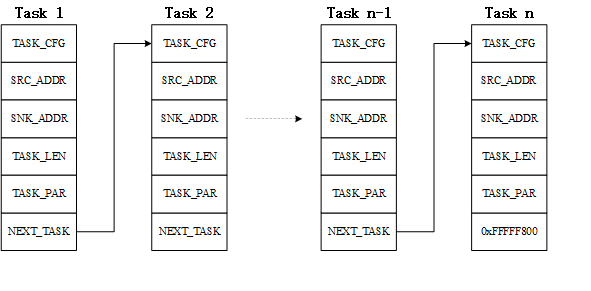

任务链表

多个任务组成任务链表,每个任务单元为 32 位,从低地址往高地址存放,具体定义如下:

- TASK_CFG1:当前任务配置,包括源端终端的 BURST 和 WIDTH 等 (外设模块的 WIDTH 需要与自身 FIFO 寄存器位宽对齐)

- SRC_ADDR:当前任务源端起始地址,注意需要 8 byte 对齐

- SNK_ADDR:当前任务终端低 32 bits 起始地址,注意需要 8 byte 对齐

- TASK_LENGTH:当前任务传输字节数,最大可设置为 32M-1 字节 (总传输长度需要与 WIDTH 对齐)

- TASK_PAR:当前任务参数,设置两个任务之间传输的延迟

- NEXT_TASK:下一任务地址,该单元配置为 “0xFFFFF800” 表示 DMA 传输结束

DMA 在工作时会读出任务相关参数更新到对应寄存器中 (软件可见)。

若需提高 DMA 带宽,建议配置起始地址和长度进行 64 bytes 对齐。

FIFO

外设DMA FIFO水位:dma_req_level ,必须满足dma_req_level= BRT × DW ÷ 8。

外设DMA FIFO水位 dma_req_level <=FIFO_SIZE(外设)-(L ÷ S) BYTE- BRT:突发 BURST 长度。

- DW:为外设使用的 DMA 数据宽度。

- L:系统时延。

- S:外设吞吐速度。

(L ÷ S) 用于解决系统时延影响,降低外设出现空满异常状态的概率,推荐dma_req_level=FIFO_SIZE/2

使用注意

- 存储器需要设置为地址递增,外设需要设置为地址保持

- 源端位宽:源端数据有效数据位宽(具体值根据DMA 相关设备推荐配置设置)

- 终端位宽:终端设备有效数据位宽(具体值根据DMA 相关设备推荐配置设置)

- 支持储存与储存传输

- 支持外设与储存传输

- 外设 DMA DATA WIDTH 设置需与外设模块寄存器位宽对齐。

- 外设 DMA TASK LENGTH 设置需要与 DMA DATA WIDTH对齐.